基于ARM的無人機飛行控制系統的研究實現

一、引言

本文引用地址:http://www.104case.com/article/201611/316781.htm無人機飛行控制系統是一種具有高性能的自主導航、自動飛行控制、任務管理的綜合系統,需要進行大量復雜的數據處理與數學運算。飛控計算機是飛行控制系統的核心子系統,隨著航空航 天技術的發展,飛控計算機向著高精度和小型化方向發展。高精度要求無人機的制導控制精度高、穩定性好,能夠適應復雜的外界環境,致使控制算法比較復雜,計 算速度快、精度高。小型化則對控制控制系統的重量和體積提出了更高的要求,要求計算機的性能越高越好,體積越小越好。性能指標和體積限制迫切需要研制新型 的飛控計算機。

二、飛控計算機與外圍的接口設計要求

基 于ARM的飛行控制計算機的設計,關鍵在于系統整體方案設計。接口設計是一個重要環節,其質量將直接影響系統的性能,信號輸入輸出時要考慮抗干擾性,所設 計的整體方案要易于實現,對不同型號的無人機要有一定的適應性。對于要求相近的型號,應該以修改控制軟件為主,以少改動或不改動硬件設計為好,這些要求都 要在方案設計的各個環節中考慮。

首先要對無人機的飛控/導航任務和實現目標作需求分析。根據飛行要求和控制對象的復雜程度,選擇控制周期;按照控制周期內控制計算量來確定計算的類型和運算速度,并結合外部單元確定接口方案,以及對抗干擾因素的考慮,可確定整體的通訊協議和接口形式。

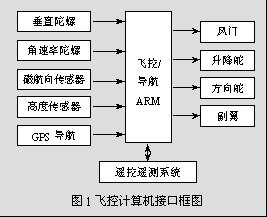

在 無人機的飛行過程中,為了實現一定的飛行任務,需要對其飛行姿態進行控制,引導飛機按照一定的航線準確飛行。為了進行姿態控制,就需要獲得飛行姿態的實時 參數信息以及遙控遙測參數。有了這些信息參數,經過計算機的控制算法計算,實時輸出控制糧到執行機構,從而實現控制/導航目的,其構成示意圖見圖1。

垂 直陀螺、三軸角速率陀螺輸出的是模擬信號,因此飛控計算機必須具有多路模擬信號的高精度采集能力。而磁航向傳感器、高度傳感器以及與GPS和遙控遙測的等 外圍單元的數據交換則采用了RS-485、RS-232通訊協議,因此飛控計算機要具有多串口的通行能力。同時系統要求一系列的電平輸出/輸入接口、舵機 接

1、ARM的選擇

從計算精度、計算速度、控制性能要求、功耗及上述接口等方面考慮, 采用ATMEL公司的AT91M55800A芯片作為CPU。該芯片集成了ARM7TDMI核、嵌入式ICE接口、存儲器以及外圍。

AT91M55800A具有先進系統總線(ASB)和先進外圍總線(APB)兩條主要總線,ASB接口由存儲控制寄存器控制用于實現最高的性能。ARM7TDMI核通過ASB接口實現與片內32位存儲器、外部總線接口(EBI)以及AMBA橋的連接。AMBA橋用來驅動APB;APB用來訪問片內外圍,優化系統功耗AT91M55800A通過完全可編程的外部總線接口直接連到片外存儲器,使讀或寫操作最快可達一個時鐘周期。8優先級向量中斷控制器和片內外圍數據控制器則顯著提高了器件的實時性能.

AT91M55800A主要硬件資源極其關鍵特性如下:

(1) 芯片提供了豐富的片上資源。有片上A/D和D/A轉換器,則系統無需外接A/D和D/A芯片,提高了系統的可靠性,減少了系統的復雜性。AT91M 55800A有片內看門狗電路,可以監測程序的意外失控。AT91M55800A芯片提供SPI總線,便于與擴展外設進行連接。

(2)集成了ARM7TDMI ARM Thumb處理核——低功耗高性能的32位RISC(Reduced Instruction Set Computer)處理器。指令功能強,采用能提供0.9MIPS/MHz的三級流水線和馮·諾依曼結構;具有能產生64位結果的增強型乘法器;尋址能力 強,有ARM指令集和Thumb指令集;嵌入式ICE,先進的軟件開發和調

試環境。

(3)8KB片內SRAM.—32位數據總線寬度,單時鐘周期訪問。

(4)完全可編程的外部總線接口(EBI)—最大可尋址空間為64MB,多達8個片選線,軟件可編程的8 位或16位外部數據總線。

(5)8優先級、可單獨屏蔽的向量中斷控制器(AIC)—7個外部中斷,包括一個高優先級、低延遲的中斷請求。

(6)58個可編程I/O口線,由PIOA和PIOB控制。

(7)6通道16位定時器/計數器,實時時鐘(RTC),系統定時器,看門狗定時器。

(8)主從式SPI接口—8~16位可編程數據長度,4個外部從芯片選擇。

(9)采用片內主振蕩器和PLL倍頻的時鐘產生器及片內32K振蕩器的實實時鐘—3MHz~33MHz頻率范圍。

(10)具有3個USART—每個USART有兩個外圍數據控制器(PDC)通道。

(11)8通道10位ADC和2通道10位DAC。

(12)先進電源管理控制器(APMC)—正常、等待、慢速、待機和掉電方式。

(13)針對所有數字引腳的JEEE 1149.1JTAG邊界掃描。

AT91M55800A上述功能和特點,使得復雜的控制算法可以在規定的時間內完成,且滿足了精度的要求。

2、存儲器的擴展

由 于AT91M55800A內部存儲器較小,所以程序和數據大多只能放在片外,因此要進行存儲器擴展。AT91M55800A的內核采用了馮·諾依曼結構。 存儲器接口可在使用存儲器最少情況下實現其潛能。速度關鍵的控制信號采用流水作業,處理速度極快。所選RAM的速度必須小于RAM的讀寫周期。在系統工作 時,程序要放在Flash中,在系統上電時由啟動代碼程序搬移到片外RAM中運行,因此選擇ROM時也要考慮存儲容量和速度。根據以上特點選擇了一片 12ns的IS61LV51216RAM組成存儲系統的RAM,一片訪問周期90ns AT49BV1604A-90TI (Flash Memory)作為程序存儲空間。此外通過SPI總線擴展一個X5045(NOVRAM),NOVRAM可在斷電后保存裝定的航跡與任務數據。

3、模擬信號的接收

垂 直陀螺、角速率陀螺、電源電壓等輸出的模擬信號首先經過信號調理模塊輸入,片上自帶的8路10位ADC已經完全滿足了系統通道數目和精度的要求,不再擴展 其他ADC器件。所采集的飛機姿態、電網電壓等信號,是飛行控制系統對無人機工作狀態進行控制和監控的基礎,同時這些信號經過編碼發往地面遙測設備,供操縱人員參考。

4、串口通信

機 上傳感器的輸出信號多數都是采用串行標準。遙控指令、遙測數據、GPS數據、高度信號、航向信號、航路裝定、控制參數設置都采用RS-232或者RS- 485接口,而AT91M55800A片內集成的3個USART不能滿足要求,必須要對串口進行擴展。完全采用軟件模擬擴展串口,將加重處理器的負荷,降 低系統的實時性。而采用16C554專用串口擴展芯片將增加系統的電路復雜性,增加電路板面積。在綜合考慮各種方案之后,將串口作如下配置:

(1) 串行口0 為遙控通道,與遙控接收機相接,接收上行信道送來的遙控信息,下傳飛機狀態參數信息,RS—232標準,波特率9600。

(2) 串行口1:通過4052 擴展,與高度傳感器和航向傳感器相接。 采用RS—485標準,波特率9600。

(3) 串行口2 與GPS接收機相接,接收GPS數據,采用RS—232標準,波特率9600。

(4) 采用SPI總線接口的USART收發器件MAX3111擴展了一路串行接口,本串行口的TX通道作為遙測通道,用于發送飛行姿態、電源電壓、發動機轉速、 任務設備工作狀態等遙測信息;RX通道為雙用途,可以作為裝定自主飛行時的預設航路用,也可以用來裝定控制參數。這樣,兼顧了系統的實時性和緊湊性

5、頻率信號的輸出

控 制伺服機構常用的是四個舵機,飛行中要求這四個舵機可以同時動作,相互之間不能有延遲。而AT91M55800A的6路定時/計數器正好可以用來作為輸出 PWM信號的器件,不需要擴展接口芯片。余下的一路定時器用作μC/OS-II的系統時鐘,另外一路定時器用作發動機轉速監測。根據舵機的工作方式和控制 精度的要求,設置工作方式,滿足舵機工作要求。這樣既減少了硬件的擴展又降低了軟件的消耗,提高了精度、大大提高系統效率。

6、數字I/O口輸出

通過AT91M55800A GI/O由片上PIOA和PIOB控制器輸出開關量,通過光耦隔離、驅動放大進行控制任務設備、回收裝置等設備。

7、復位電路

AT91M55800A 在復位時,主時鐘來自慢速時鐘(32 768Hz),并且主時鐘上的信號必須在NRST信號上升沿之前至少10個時鐘周期內保持有效,及復位信號至少保持0.3ms,所擴展的存儲系統復位時間 均小于0.3ms,因此本系統采用了能提供20ms低脈沖的MAX6315芯片。同時AT91M55800A具有可編程的看門狗定時器。由于系統電源瞬間 欠缺或意外掉電致使程序跑飛或重要數據丟失導致系統無法工作時,采用看門狗定時器可產生內部復位信號,使復位系統。

四、系統設計中的關鍵技術

1、硬件資源的合理利用和端口配置的原則

AT91M55800A 有著豐富的硬件資源,能否充分利用和恰當配置這些資源是設計成敗的關鍵。如果給CPU的負擔過重,系統有可能難以完成實時控制的任務,如果配置不合理,資 源則不能得到充分利用,而且會影響系統的實時性,增添軟件的復雜性。CPU主要處理4路模擬量輸入、10路開關量輸入、1路頻率量輸入、3路定時信號輸 入、4路PWM波輸出、8路開關量輸出和4路串行數據接口,根據微控制器的結構特點分別配置,如將模擬量輸入配置在A/D部分,開關量輸入和輸出配置在 GPI/O,3路定時信號輸入、1路頻率量輸入和PWM波配置在定時/計數器多通道部分,4路串行數據接口通過適當擴展配置在3個USART上。在設計中 對端口分配遵循了以下原則,并做了一定的時間測算;

(1) 首先確定MCU內核的實現方案,為輸入輸出信號量連接方案的確定開創條件;

(2) 優先考慮各端口的基本功能,再次考慮端口的第二、第三功能;

(3) 考慮信號匹配與端口的驅動能力;

(4) 考慮時間因素,對ADC、UARST、GPI/O、PWM、SPI等處理子程序進行時間估計與測算,確定CPU的任務量,保CPU有一定的時間裕度;

(5) 利用空余的端口做冗余設計,使某些功能的實現有一定的自由度。

2、系統的抗干擾措施

在無人機系統性能諸指標中,可靠性是首要考慮的因素。無人機飛行控制器必須穩定可靠地運行,否則將導致控制出現偏差,嚴重時將可能造成巨大經濟損失或者生命危險。因此在控制器硬件的設計中,要始終貫徹高可靠性、高穩定性這一原則,并為軟件抗干擾措施的實施打好基礎。

影響控制器可靠安全運行的主要因素有以下幾個方面:電磁場干擾、供電方式、元器件性能、PCB的布局與走線、機械結構設計等。

針對這些因素,在本系統的硬件設計中采用了如下一些措施:

(1)主控板采用四層的高頻電路板;

(2)采用濾波技術、去耦電容、屏蔽技術、隔離技術和接地技術減小電磁場的干擾;

(3)數字部分和模擬部分獨立供電

(4)盡量選用高集成度、高穩定性、高可靠性的面貼元件;

(5)PCB板上元器件按功能分區、就近布局,45°走線、滿接地;

(6)選擇高可靠性接插件,緊固安裝,屏蔽殼體。

3、整機供電與功耗考慮

無 人機的動力源是能量有限的機載蓄電池,所以能耗問題是衡量控制其性能的一項指標。機載蓄電池提供的是±12V的直流電源,對于飛控器來說,需要解決兩個問 題。一是如何進行DC/DC轉換既能滿足系統對電源數量及伏值的要求,又使轉換效率足夠高;二是選用什么樣的元器件,既能滿足信號匹配的要求又能使器件功 耗低。

系 統中選用的是高轉換效率的小型PKC2121模塊,可以產生穩定的±12V電壓,為±9V的電源基準提供輸入,5V和9V根據具體需要給模擬電路供 電,5V作為3.3V電源基準REF192GS的輸入電壓,3.3V給飛控計算機供和存儲系統供電。在信號匹配的前提下盡量選用低功耗的CMOS器件,降 低系統總能耗。

五、結束語

經 過初步調試,該硬件平臺各項功能均達到設計目的。為了方便和硬件的聯調,軟件設計以源碼公開的實時嵌入式操作系統μC/OS-II為軟件平臺,將系統功能 按照優先級循序分為數據采集模塊、控制解算模塊、模態控制模塊、高度航向讀取模塊、指令接收模塊、 GPS接收模塊、航路控制模塊、遙測發送模塊、芯片啟動部分選用匯編語言,對算法復雜、計算量大的,采用C語言。軟件和硬件分別調試通過后,可進行軟件和 硬件的聯調,最后形成基于ARM的新型飛行控制計算機。

該硬件系統體積小,成本低。設計中采用了模塊化的結構形式,將主控模塊和信號調理模塊及信號輸出模塊分開,那么將主控模塊與不同的信號調理模塊和輸出信號的相結合可以實現設計系統的通用性作為某型號的一系列無人機的飛控器。隨著技術的不斷發展 ,ARM將以它特有的優越性在軍事和高科技中得到廣泛的應用。

參考文獻:

[1] David Seal. ARM Architecture Reference Manual Second Edition [M]. Pearson Education Limited.

[2] ARM7TDMI (Rev4) Technical Reference Manual[M]. ARM DDI

[3]張明廉.飛行控制系統[M]. 北京:航空工業出版社, 1993

[4]何衍慶等. 控制系統分析、設計和應用[M]. 北京:化學工業出版社. 2003.1

[5]馬忠梅等. ARM嵌入式處理器結構與應用基礎[M]. 北京:北京航空航天大學出版社.2003

評論