STM32F7有別于其它相同內核MCU的幾個特色

一般來講,基于ARM®Cortex®-M7內核的微控制器大多具有相似的處理器配置選項。通常包括:

-一個64位AXI系統總線接口

-一個指令和數據高速緩存

-64位指令緊耦合存儲器(ITCM)

-雙32位數據緊耦合存儲器(DTCM)

不過,本文只是從應用開發的層面介紹STM32F7系列有別于其它使用Cortex-M7內核的MCU的幾個特色。

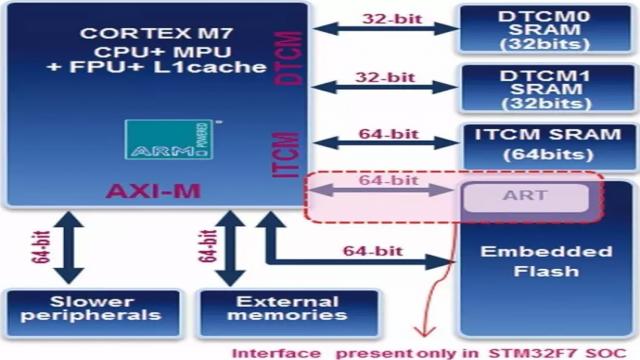

首先,第一個重要特色在于STM32F7器件同時具有ITCM接口和AXI接口連接到片內閃存,如圖1所示。

圖1:基于ARMCortex-M7內核的系統級芯片的框圖

ITCM和AXI雙接口的存在使得執行代碼時具備更大的靈活性。此外,STM32F7還有一個稱為自適應實時加速器(ARTAccelerator™)的內置閃存加速器,從而實現閃存零等待執行。使用TCM接口和ART加速器能能實現與帶緩存AXI接口相似的性能。同時用戶代碼也不會有高速緩存失效或高速緩存維護操作的麻煩。

利用ART Accelerator加速引擎和高達16kB的L1緩存,STM32F7MCU可實現ARM Cortex-M7的最佳性能。不管是從片內閃存還是外部存儲器執行代碼,在216MHz下均可達到1082 CoreMark/462 DMIPS。

第二個重大特色在于內部SRAM分布在不同的模塊中,以降低動態功耗,并允許從各個總線主機同時訪問不同的SRAM模塊,以優化帶寬和延遲。

此架構的一個典型應用實例就是人機界面,在人機界面中,音頻和圖形數據與系統RAM之間的傳輸必須同時進行。

第三個就是它的高級浮點單元。STM32F7系列器件具有一個高性能的單或雙精度浮點單元(FPU),支持所有ARM單或雙數據處理指令和數據類型。FPU在需要浮點數學精度的許多應用中提供了優勢,包括環路控制、音頻處理、音頻解碼和數字濾波等。

它還有個額外優勢,那就是將某些功能的執行或處理可以從CPU分流到FPU,使CPU用于其他任務。它支持雙精度,因此更易于使用雙精度浮點指令的基于PC的數學軟件。

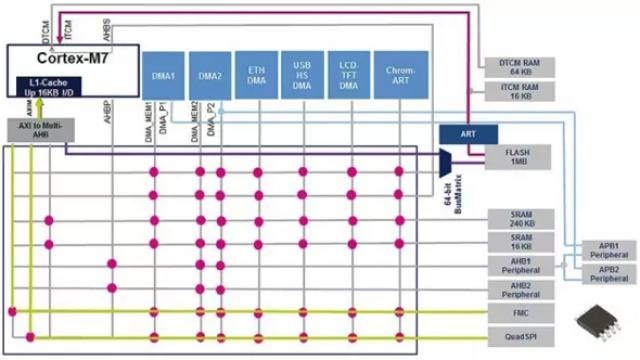

第四,STM32F7 MCU最具特色的設計之一是它們的智能系統架構,它使用兩個子系統,如圖2所示:

圖2:STM32F7微控制器的總線矩陣

AXI-to-multi-AHB橋將AXI4協議轉換成AHB-Lite協議

multi-AHB總線矩陣管理主機之間的訪問仲裁

該仲裁使用循環調度算法保障主機對從機的訪問,即使多個高速外設同時工作,也能實現同時訪問并高效運行。

最后,不得不提它的L1高速緩存。STM32F7嵌入了指令和數據高速緩存,當從片上或片外存儲器讀取代碼和數據時可彌補插入等待狀態,從而提高性能。當然,如果出現高速緩存失效和高速緩存行填充,此時查看高速緩存將無法保證數據的確定性。

這就是為什么要強烈推薦使用TCM存儲器來執行關鍵代碼、存儲關鍵數據的原因。這在必須保證安全操作的應用中(如家電和電機)通常都很有用。

由于高速緩存不僅可以由CPU訪問,也可以通過其他主機進行訪問(包括直接存儲器訪問(DMA)控制器),因此需要軟件維護操作。訪問物理存儲器時,這些主機可能會讀出過期的數據,而更新的數據在CPU高速緩存中已可用。

為了避免這個問題,開發者編寫用戶代碼時應該采取以下措施:

A.當除CPU以外的主機將執行對高速緩存的訪問之前,推薦進行高速緩存清零。這是為了確保CPU的最新的更新數據被寫回到物理存儲器。

B.當除CPU以外的主機對高速緩存數據進行了更新后,在對高速緩存進行讀操作之前,CPU應該使高速緩存失效。這是為了確保從物理存儲器的直接讀取。

C.有時也需考慮無高速緩存操作。當高速緩沖存頻繁被其他主機訪問時,可以通過CPU配置不可緩存屬性防止數據的不一致性。

評論