ADC噪聲來自何處?

雖然交錯式ADC具有極佳的速度和帶寬性能等優勢,而除此之外交錯式ADC仍存在一些問題和不足之處。

這些問題主要圍繞ADC的噪聲源展開。 評估ADC噪聲的具體情形時,噪聲進入ADC的方式是最具參考價值的。因此,噪聲進入ADC并體現在輸出數據的FFT中時,所通過的入口類型則是需要系統設計師進行深入了解的。

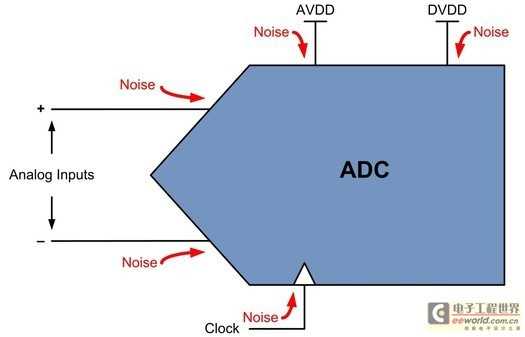

可將ADC大致視為混頻器。如果有噪聲從任一入口進入ADC,就會在輸出數據的FFT中表現出來。 如圖1所示,噪聲可通過電源輸入端、模擬輸入端和時鐘進入轉換器。

ADC噪聲“入口”

由于此處的噪聲一詞含義比較模糊,可以先根據所討論的ADC輸入(入口)來明確其含義。

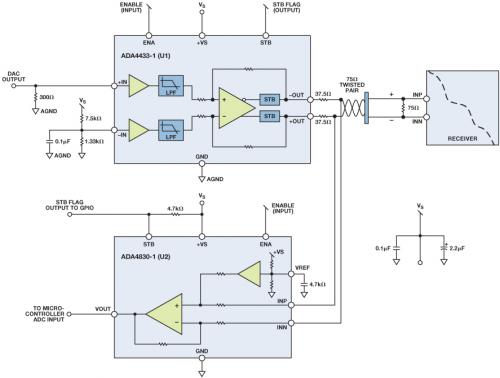

電源輸入端是噪聲的通道,噪聲可由此進入ADC并體現在輸出數據的FFT中。這種情況下,有幾種方法可以評估該噪聲及其對ADC性能的影響。ADC設計應該做到器件本身就可衰減來自電源的噪聲輸入。這里用于評估電源端噪聲的度量方式是電源抑制比(PSRR)和電源調制比(PSMR)。通過測量這兩個參數,可以了解到ADC對電源輸入端噪聲的處理能力。

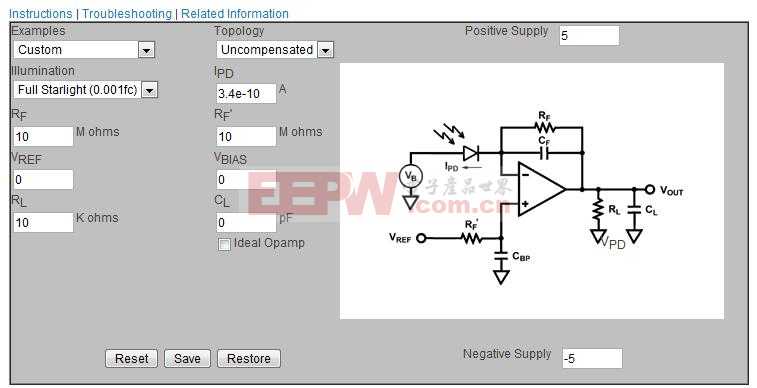

首先,針對ADC的模擬輸入端,必須將噪聲分成兩種類型進行分析。首先,一般寬帶噪聲會通過模擬輸入端進入轉換器,并且通常源于信號鏈中位于ADC之前的器件。系統設計師可為ADC選擇噪聲極低的驅動放大器,但仍會有一定的噪聲被放大并輸入ADC。

為克服這一問題,通常會在ADC輸入端添加一個抗混疊濾波器(AAF)。這有助于濾除可能進入ADC的大部分寬帶噪聲,并且最后會在ADC的信噪比(SNR)中體現出來。除寬帶噪聲外,雜散成分和諧波也可能通過模擬輸入端進入ADC。這些也可通過AAF濾除。這將通過ADC的無雜散動態范圍(SFDR)反映出來。 具有良好的AAF設計對處理這些狀況非常重要。

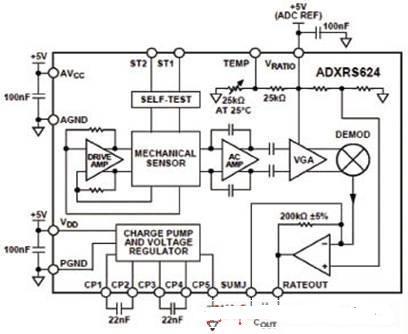

圍繞ADC需要闡述的最后一個噪聲入口為時鐘輸入端。該輸入端與模擬輸入端類似,寬帶噪聲以及雜散和諧波成分可由此進入ADC并體現在輸出數據的FFT中。確保選擇合適的時鐘輸入驅動器來為ADC提供干凈的低抖動輸入時鐘,這點非常重要。

該時鐘信號應以特殊方式連接至ADC,使其不會耦合能夠進入ADC的噪聲。與模擬輸入端類似,可在時鐘輸入端添加濾波器來幫助濾除原本可能通過時鐘輸入端進入ADC的噪聲。 同樣,與模擬輸入端類似,通過時鐘輸入端的噪聲機制可通過ADC的SNR和SFDR性能表現出來。

使用ADC設計系統時,必須考慮到所有這些入口。經測試發現,應該將ADC作為混頻器對待,它會將通過上述任一入口進入的各種噪聲成分混合到輸出數據上的FFT中。顯然,系統設計師希望ADC的輸出端只出現所需的信號。為了做到這一點,設計師必須在這些輸入端采取適當措施,確保將噪聲降至最低,使其無法通過這些入口進入。

評論