基于PCI總線的四通道CAN通訊卡的設(shè)計

摘要:為了完成核電現(xiàn)場I/O模塊和控制站之間的數(shù)據(jù)傳輸,設(shè)計了一種基于PCI總線的四通道CAN通訊卡,每個CAN通道連接32個單通道I/O模塊,每隔25 ms采集I/O模塊的數(shù)據(jù)一次,該系統(tǒng)的數(shù)據(jù)采集總量為400個模擬量和112個開關(guān)量。本設(shè)計采用兩個CPU,使每個中斷服務(wù)時間占用中斷間隔的百分比提高了19%。本文重點闡述了具體的硬件電路設(shè)計,包括原理設(shè)計、芯片選型、PCB制作等,具有高速度和低成本的優(yōu)點。

本文引用地址:http://www.104case.com/article/201610/306142.htm關(guān)鍵詞:PCI總線;數(shù)據(jù)采集;CAN通訊;雙口RAM

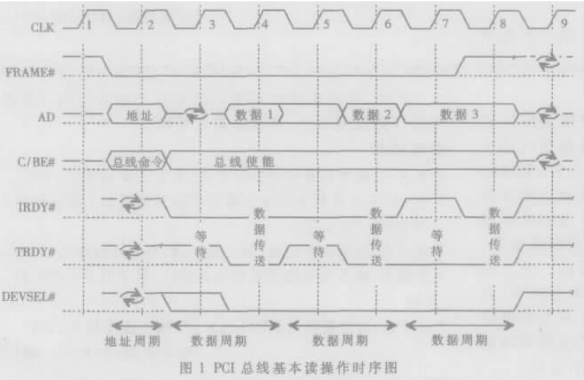

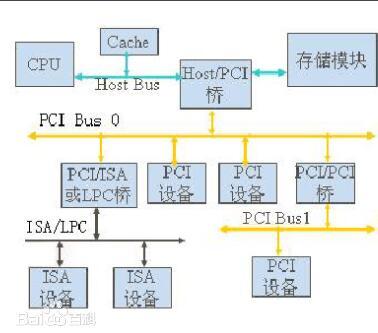

PCI總線(peripheral component interconnect)俗稱外部部件互聯(lián)總線,是由美國Intel公司率先提出的一種先進的高性能局部總線,不依附于某個具體的處理器。比起IS A、EISA和MC等標(biāo)準(zhǔn)總線,更能滿足人們對微機系統(tǒng)I/O帶寬的要求。PCI總線的時鐘頻率為0~33 MHz,其最大數(shù)據(jù)傳輸速率可達到528 Mbps,PCI局部總線的引入,打破了數(shù)據(jù)傳輸?shù)钠款i,使數(shù)據(jù)的實時高速采集和傳輸成為可能。CAN總線是一種全數(shù)字化、雙向和多主的現(xiàn)場總線,具有通信速率高、容易實現(xiàn)、且性價比高等優(yōu)點,應(yīng)用廣泛。

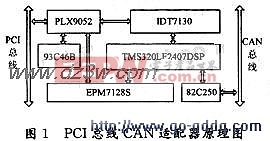

1 CAN通訊卡的設(shè)計原理

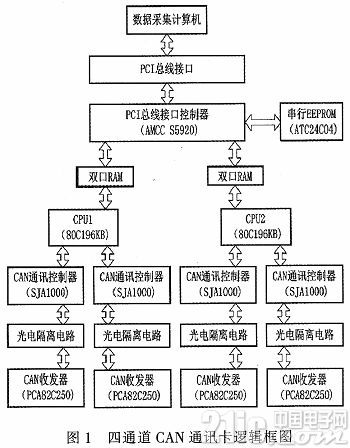

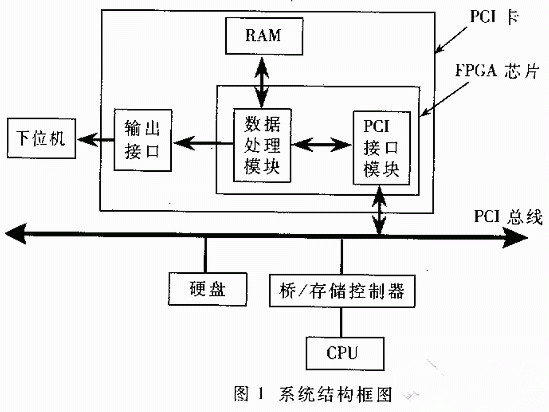

四通道CAN通訊卡介于核電現(xiàn)場I/O模塊和主站之間,是一塊基于PCI總線的高速數(shù)據(jù)采集卡。一塊通訊卡上有4個CAN通道,每個 CAN通道連接32個單通道I/O模塊。每隔25 ms采集I/O模塊的數(shù)據(jù)一次,通過CAN通訊接口傳送到微控制器80C196KB,經(jīng)過處理后再通過8K*8的雙口RAM經(jīng)由PCI總線控制器上傳給主機。主機對I/O模塊的初始化、對時等操作由80C196KB通過CAN通訊下傳到單通道I/O模塊。其具體的邏輯框圖如圖1所示。

根據(jù)核電站試驗數(shù)據(jù)采集系統(tǒng)的設(shè)計規(guī)范,該系統(tǒng)的數(shù)據(jù)采集總量為400個模擬量和112個開關(guān)量。每個采集模塊采集一個點,因而共有512個采集模塊,這些采集模塊分布在兩個機柜中。所有這些采集模塊的數(shù)據(jù)都是通過CAN總線分別傳送到數(shù)據(jù)采集柜中的兩臺數(shù)據(jù)采集計算機,進行量程轉(zhuǎn)換和相關(guān)處理,送到數(shù)據(jù)處理計算機。每臺數(shù)據(jù)采集計算機上有2塊4通道智能CAN總線通訊卡,即8條CAN總線通道,分別將兩個機柜的采集信號轉(zhuǎn)到數(shù)據(jù)采集計算機上進行處理。因而每根CAN總線傳送32個采集模塊的數(shù)據(jù)。

鑒于四通道CAN通訊卡的數(shù)據(jù)采集功能,該卡的工作流程是:CPU每隔25 ms(最小巡檢周期)掃描四條CAN總線上的128個采集模塊的數(shù)據(jù),經(jīng)過處理后送給PCI總線,最后到達數(shù)據(jù)采集計算機。

由于CAN卡的數(shù)據(jù)采集量比較大,根據(jù)掃描周期,對CPU而言,每秒鐘由CAN總線控制器產(chǎn)生的中斷有32*4*1 000/25=5 120個,則每個中斷之間的間隔為1 000 000/5120= 195.3μs。這對于CPU提出了很高的要求。如采用一個80C196KB,由于其單指令周期為0.125μs,假設(shè)每個中斷服務(wù)指令需300條匯編指令,平均每條匯編需兩個單指令周期,即0.25μs,則每個中斷服務(wù)程序需300*0.25=75μs,占用這個中斷間隔的 75/195.3=38.4%。這些數(shù)據(jù)表明即使處理速度滿足要求,CPU的資源也是比較緊張的。若采用兩個80 C196KB,則每個CPU處理的中斷為5 120/2=2 560,每個中斷之間的間隔195.3*2=390.6μs,每個中斷服務(wù)程序時間占用這個中斷間隔的75/390.6=19.2%,這對每個CPU而言,就輕松多了。

根據(jù)上述分析,決定采用兩個CPU(分別稱為CPU和從CPU)。從CPU只負責(zé)采集兩個CAN通道數(shù)據(jù),通過雙口RAM向主CPU發(fā)送采集的數(shù)據(jù)。主 CPU不僅負責(zé)采集兩個CAN通道數(shù)據(jù),還負責(zé)和PCI總線接口,將從CPU采集的數(shù)據(jù)和自身采集的數(shù)據(jù)一起向PCI總線傳輸。同時,主CPU接收到 PCI總線上的命令字和數(shù)據(jù)后,還需通過雙口RAM將它們傳送給從CPU,以確保主、從CPU進行數(shù)據(jù)采集的一致性和完整性。

2 芯片介紹

2.1 PCI總線控制器

PCI總線控制器采用AMCC公司的S5920,S5920是符合PCI2.2規(guī)范的從方式接口控制器,他只能工作于從方式(slave)。Add-On 側(cè)有兩種工作方式:郵箱方式(MAILBOX)和直通方式(PASS—THRU)方式。PASS—THRU方式又分PASSIVE和ACTIVE方式。根據(jù)各種方式的側(cè)重點不同,我們采用PASS—THRU的ACTIVE方式。它操作簡單,對時序要求較少,比較適合大量數(shù)據(jù)的傳輸。四通道CAN通訊卡的資源申請采用非易失性RAM(NVRAM)——串行EEPROM AT24C04來實現(xiàn)。

2.2 CPU

采用Intel的16位微控制器80C196KB,它是Intel公司性能最強的CMOS芯片,其片內(nèi)集成有8路A/D轉(zhuǎn)換器,包括一個 8通道多路模擬開關(guān),采樣保持電路和10位A/D轉(zhuǎn)換器。與96系列微控制器相兼容,并增加了許多新功能。具有高速I/O子系統(tǒng)、中斷源及中斷向量顯著增加(28個中斷源,18個中斷向量),可動態(tài)配置8位或16位總線寬度。

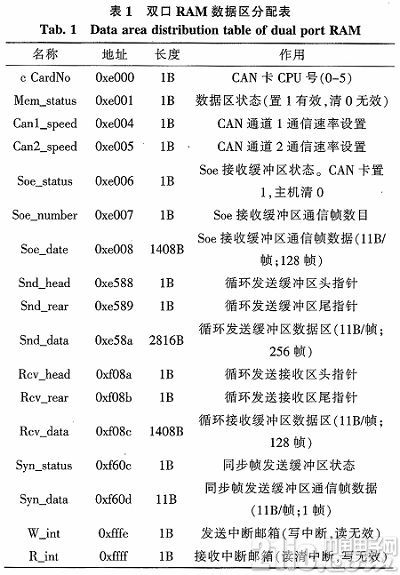

2.3 雙口RAM

接口卡含有板級CPU總線和主站ISA總線。兩條總線通過8K*8的雙口RAM交換數(shù)據(jù)。通過雙口RAM,主站直接控制接口卡、并與其交換靜態(tài)數(shù)據(jù),主站和接口卡協(xié)調(diào)的依據(jù)是郵箱命令。雙口RAM的詳細內(nèi)存地址分配如表1所示。

2.4 CAN通訊接口

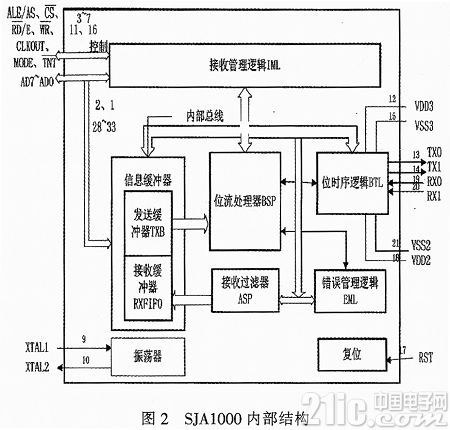

CAN控制線采用Philips公司的SJA1000,它與PCA82C200管腳兼容。具有擴展的接收緩沖器,64字節(jié)的FIFO結(jié)構(gòu),支持CAN2.0B協(xié)議。24 MHz晶振頻率下,傳輸速率高達1.M bits/s。其內(nèi)部結(jié)構(gòu)如圖2所示。物理傳輸層采用EIA RS485,故采用高速光電隔離器件HCPL0611,保證電氣上無干擾,隔離電壓達到500 V以上,提高整個系統(tǒng)的測量精度。收發(fā)器采用Philips公司的PCA82C250芯片,其可以提供對總線數(shù)據(jù)的差動發(fā)送能力和對通信總線數(shù)據(jù)的差動接收能力。

2.5 譯碼電路

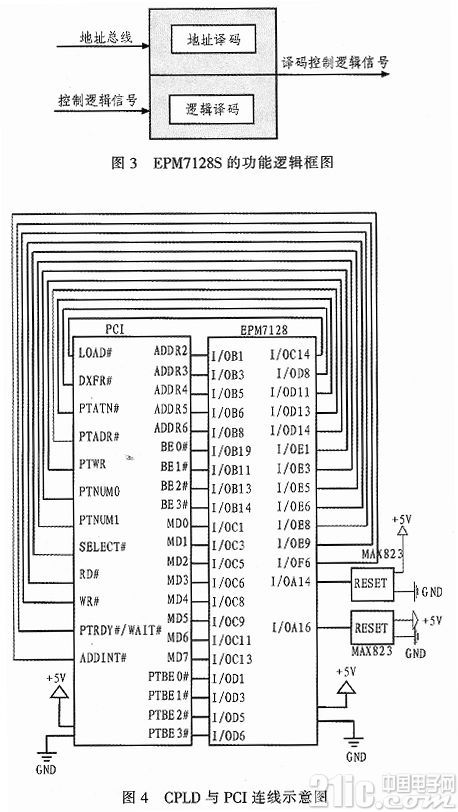

譯碼電路采用ALTERA公司的EPM7128S CPLD。它具有高阻抗、電可擦等特點,可用門單元為2 500個,管腳間最大延遲5 ns,工作電壓5 V,輸入輸出線數(shù)84,并且它集邏輯譯碼、總線接口等于一體,十分方便。圖3為EPM7128S的功能邏輯框圖,其與PCI總線的連接示意圖如圖4所示。

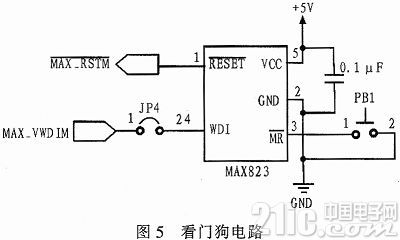

2.6 微處理器監(jiān)控故障自復(fù)位電路

復(fù)位電路采用MAXIM公司的MAX823看門狗電路,如圖5所示,以它為核心可以完成以下幾項功能:

1)上電和手動復(fù)位;

2)監(jiān)視定時器(看門狗)復(fù)位。

單排兩針跨接器JP3、JP4分別用于2個80C196KB的電源監(jiān)控和硬件看門狗復(fù)位。跨接表示允許看門狗復(fù)位,否則禁止看門狗復(fù)位。

3 CAN通訊卡的PCB設(shè)計

在設(shè)計PCB時,我們采用Mentor Graphics公司的PADS2005軟件,它包括整個完整的PCB設(shè)計過程,涵蓋了從原理圖網(wǎng)表導(dǎo)入,規(guī)則驅(qū)動下的交互式布局布線,DRC/DFT/DFM檢查與分析,直至最終Gerber生產(chǎn)文件、裝配及物料清單輸出等全方位的功能需求。良好的PCB設(shè)計不僅可以增加PCB的視覺美感,更能提高系統(tǒng)的抗干擾能力。在數(shù)據(jù)采集卡的PCB制作中,要考慮插卡的高頻性能、電源去耦與干擾的抑制、接地方式的選擇等因素。

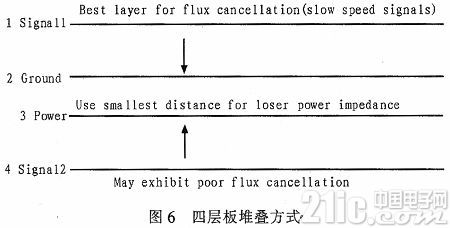

3.1 PCB層數(shù)的選擇

在制作PCI板卡時,選擇制作四層的PCB板,其堆疊方式如圖6所示,這樣因使用了Power及Ground平面層,EMI之特性有很大改善。

3.2 去耦電容

由于一些高速信號,噪聲頻率比較高,我們采用0.1μF的電容作為去耦電容,并使之盡量靠近IC的電源地管腳,使其與電源和地之間形成的回路最短。對于從外部連接器進來的信號線使用的旁路電容,要靠近連接器放置,以減小外部連接線可能引入的干擾在板上傳播。

3.3 電源設(shè)計

為了防止數(shù)字器件所帶來的高頻噪聲對模擬器件造成影響,將模擬信號的地與數(shù)字信號的地的走線分開,然后在PCB上找一個適當(dāng)?shù)奈恢脤烧邌吸c連通。系統(tǒng)的模擬地和數(shù)字地的共地點一般選擇ADC芯片上引腳所需電流最大的地方,以便使大電流對地回流路徑最短,減少對模擬電路的電磁干擾,提高系統(tǒng)精度。因為快速的數(shù)字振蕩可能將轉(zhuǎn)換噪聲禍合到模擬電源中,所以模擬電源和數(shù)字電源應(yīng)該分開供電。在數(shù)據(jù)采集卡的設(shè)計中,模擬電路直接由DC—DC隔離電源供電,數(shù)字電源直接由PCI插槽中的+5V和+3.3V供電。

3.4 走線要求

PCI總線的32位部分的所有信號最大走線長度必須限定在1 500 mil以內(nèi),PCI時鐘信號線的長度必須是2 500 mil(±100 mil),并且只能和插卡上的一個負載連接。該引線只能在PCB一面走線且在轉(zhuǎn)角處用弧形,切忌用直角,銳角,可用“蛇”形走線來滿足長度要求。

另外,對于電源線和地線的線寬,通常是地線比電源線窄,即:信號線電源線地線,信號線寬通常為:0.2~0.3 mm,電源線為1.2~2.5 mm。地線盡量采用大面積覆銅的方式來增大地線面積減小接地阻抗,提高電路板的抗干擾能力。

3.5 時鐘信號的保護

為了滿足高速數(shù)字信號的要求,PCB布線要求滿足盡量減少傳輸延遲、減少信號損耗等。數(shù)據(jù)采集板上PCI時鐘信號和AD采樣、鎖存、FIFO的讀和寫這些頻率較高的時鐘信號,應(yīng)在PCB布線時在兩邊設(shè)置地線加以保護。

4 結(jié)束語

使用基于PCI總線的高速數(shù)據(jù)采集卡是現(xiàn)代信號處理中實現(xiàn)實時數(shù)據(jù)進機存儲的重要方法。本方法所設(shè)計實現(xiàn)的數(shù)據(jù)采集系統(tǒng)也可應(yīng)用于通信振動工程、語音處理、工業(yè)自動控制以及生物醫(yī)學(xué)工程領(lǐng)域。目前我國的數(shù)字化儀控系統(tǒng)還處于初級階段,核電站數(shù)字化儀控系統(tǒng)的國產(chǎn)化是我國核電儀控事業(yè)發(fā)展的必由之路。該高速數(shù)據(jù)采集卡將應(yīng)用在嶺澳核電站BOPLOT KDO/KME項目中,完成現(xiàn)場I/O模塊和控制站之間的數(shù)據(jù)傳輸,每隔25 ms采集一次數(shù)據(jù),實現(xiàn)了高速度和低成本的優(yōu)點。

評論