基于MPC8280的PCI驅動設計

摘要 芯片MPC8280的主頻最高為450 MHz,僅靠運行在其上的軟件雖可實現路由交換功能,但交換容量僅約為40 Mbit·s-1,無法滿足多路千兆交換性能要求。利用MPC8280的PCI口外接千兆交換芯片BCM56514,能突破這一性能瓶頸。基于MPC8280的PCI驅動,使得MPC8280通過PCI卻嬋占潿列床僮鰲⑴渲每占潿列床僮骱I/O空間的讀寫操作,并實現對BCM56514的配置、控制及路由表的更新,從而使MPC8280在路由交換領域得以應用。

本文引用地址:http://www.104case.com/article/201609/305032.htm近年來,多媒體通信技術應用迅猛發展,對網速的要求也迅速提升。為適應這一趨勢,與網絡相關的終端設備和路由交換設備的性能均亟需提升。在當今中國,計算機作為網絡終端設備,網口的標配速率已由100 Mbit·s-1改為1 000 Mbit·s-1,交換機、路由器等作為路由交換設備,交換容量量級也由原來100 Mbit·s-1上升到1 000 Mbit·s-1甚至10 Gbit·s-1。MPC8280是由Freescale公司推出的雙地址總線雙處理器芯片,自其推出以來,因其豐富的外圍接口已在航空航天、通信電子、醫療器械、交通設施等領域得到廣泛應用,然而在今日迫切需求的大容量路由交換領域,卻因其最高主頻為450 MHz的限制,依靠運行在MPC8280上的軟件扣除中斷處理、系統管理等開銷外,實現的交換容量僅為40 Mbit·s-1,在多路千兆交換應用中存在性能瓶頸。利用MPC8280的PCI口外接千兆交換芯片BCM56514,使得運行在MPC8280上的軟件僅作路由計算和路由表的維護,而將交換控制交由BCM56514實現,可突破性能瓶頸。完成PCI驅動設計是這一方法能得以實施的先決條件,MPC8280通過PCI內存空間讀寫操作、配置空間讀寫操作和I/O空間讀寫操作,實現對交換芯片的配置、控制及路由表的更新,從而使MPC 8280在大容量路由交換領域得到成熟應用。

1 PCI知識介紹

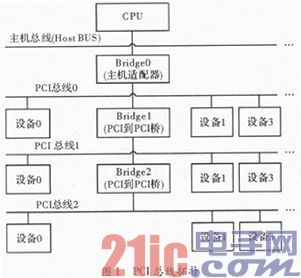

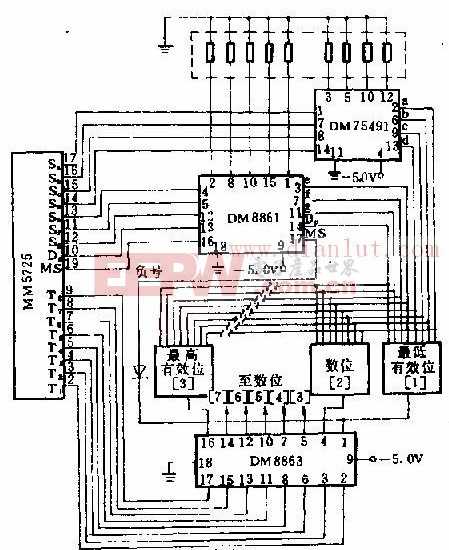

PCI為Peripheral Component Interconnect的縮寫,是一種總線規范,用于外圍設備互聯。目前使用2.2版本的PCI規范。主要由時鐘信號(PCI_CLK)、控制信號 (FRAME、IRDY、DEVSEL、TRADY、STOP、IDSEL)、地址數據復用信號AD[31:0]及校驗和錯誤指示信號(SERR、PERR)構成。地址和數據信號可擴展到64 bit,時鐘信號常用33 MHz,可擴展到66 MHz,速率可達528 MByte/s。采用分段分層結構,其總線拓撲結構如圖1所示。

2 PCI驅動設計

PCI驅動通過配置寄存器,完成總線初始化,并提供PCI配置空間讀寫、PCI內存空間讀寫、PCI I/O空間讀寫和中斷函數接口。上層應用利用這些操作接口發現外部交換芯片,并能獲取交換芯片信息,實現對外接交換芯片的配置管理、路由表更新、狀態回讀等操作,最終實現PCI驅動設計。

2.1 PCI驅動流程設計

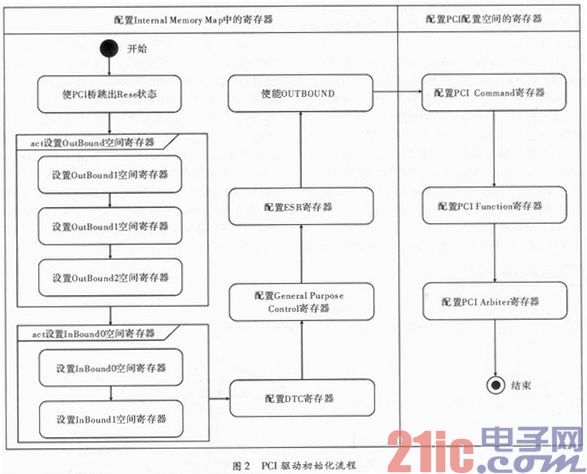

首先通過設置寄存器,使芯片跳出PCI重啟狀態,接著根據系統的地址分配對Outbound和Inbound寄存器組進行配置,然后對PCI使用的字節序、錯誤狀態和Master模式進行配置,最后使能PCI內存空間讀寫和配置空間讀寫。使用UML的活動圖對PCI驅動流程設計建模如圖2所示。

2.2 配置空間讀寫設計

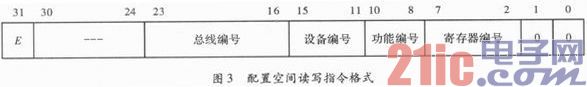

指令按照一定的數據格式優先寫到CONFIG_ADDR寄存器,然后通過向CONFIG_DATA寄存器填入數據,完成寫操作,或從CONFIG_DATA讀出數據,完成讀操作。無論CONFIG_ADDR寄存器的數據是否需要改變,每次操作都必須先對CONFIC_ADDR寄存器操作,然后才可對CONFIC_DATA寄存器操作,否則操作無效。指令數據格式如圖3所示。

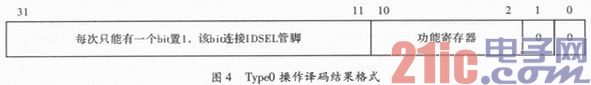

配置空間操作時,地址譯碼過程如下:例如Device Number為0b01011時,對應的十進制數為11,則Bit[31:11]中的Bit11置1,其他Bit為0,此時在硬件上將IDSEL信號連接到Bit11的PCI設備將被選中;若Device Number為0b01100時,對應的十進制數為12,則Bit[31:11]中的Bit12置1,其他Bit為0,此時在硬件上將IDSEL信號連接到Bit12的PCI設備將被選中;Device Number的特殊定義如下;0b01010將選定Bit[31];0b11111將執行特別操作;0b00000將對PCI橋自身進行操作。譯碼結果的格式如圖4所示。

共有兩種操作類型:了ype 0操作和Type1操作。Type0操作適用于目標設備和PCI橋在同一總線上,PCI橋直接根據從上層總線接收到指令中的Device Number進行地址譯碼,并將Bit[31:11]數據中對應的Bit置1,Bit[1:0]設置成0x00,在PCI總線配置操作的地址時段,將譯碼結果發送到PCI總線的AD[31:0]上。

Type1操作適用于目標設備和PCI橋不在同一總線上,需經過PCI橋將完整的數據繼續向下傳遞。當PCI橋在配置空間操作的地址時隙從AD[31:0]收到指令時,判斷目標設備是否在其負責的范圍內,若不在,將不處理。若在,則將AD[31:0]的數據和PCI_C/_BE完整的向下傳遞;若發現目標設備為本層設備,將操作變為Type0操作,選中目標設備。

2.3 內存空間讀寫設計

MPC8280的PCI內存讀寫分為MPC8280主動發起的PCI內存空間讀寫和MPC8280被動引起的PCI內存空間讀寫。在進行PCI內存空間讀寫時,需地址譯碼。

MPC8280主動發起的PCI內存空間讀寫,MPC8280側地址譯碼流程如圖5所示。先對操作地址進行判斷,若落在MPC8280的內部存儲器映射寄存器(IMMR)范圍內,接著就需判斷是否落在PCI寄存器,根據判斷結果決定是否對PCI寄存器進行操作或不做處理。若不是落在MPC8280的IMMR范圍,需判讀是否落在PCI OutBound空間,若落于PCI OutBound空間,則需根據寄存器的配置,對地址進行譯碼,并將譯碼后的結果在地址時隙被發送到PCI總線的地址管腳,若未落在PCI OutBound空間,卻落于PCIBR0或PCIBR1寄存器定義的范圍內,則將地址直接通過地址時隙發送至PCI總線的地址管腳。

評論