基于MAX 7 0 0 0A與CYUSB3014的USB3.0數(shù)據(jù)采集系統(tǒng)

0 引言

本文引用地址:http://www.104case.com/article/201609/304017.htm目前高速數(shù)據(jù)采集技術(shù)越來越得到人們的重視,傳統(tǒng)的USB 2.0采集平臺(tái)理論帶寬只有480 Mbps,實(shí)際傳輸能力只有30 Mb/s左右,而USB 3.0采集平臺(tái)理論帶寬達(dá)到了5Gbps,能有效解決USB2.0采集系統(tǒng)的缺陷。目前一些采集系統(tǒng)采用單片機(jī)為主控芯片,則不能充分發(fā)揮USB3.0的帶寬,性能不佳。本文研究和設(shè)計(jì)了一套基于USB3.0總線的數(shù)據(jù)采集系統(tǒng),此系統(tǒng)采用高速CPLD芯片MAX7000A作為主控芯片,CYUSB3014作為USB3.0主機(jī)接口芯片,能實(shí)現(xiàn)超高速實(shí)時(shí)數(shù)據(jù)采集與傳輸。

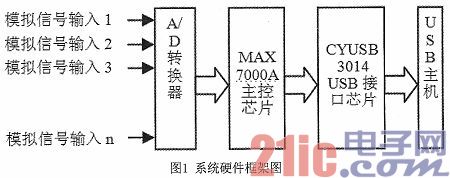

1 系統(tǒng)硬件設(shè)計(jì)

系統(tǒng)的總體框架如圖1所示。被采集的信號(hào)通過相應(yīng)的傳感器轉(zhuǎn)換為相應(yīng)的模擬電壓,A/D芯片將其轉(zhuǎn)換為數(shù)字信號(hào),再送到CPLD主控芯片MAX7000A,經(jīng)處理后發(fā)送到USB 3.0主機(jī)接口芯片CYUSB3014,該芯片工作在SLAVE FIFO模式,最后數(shù)據(jù)以5Gbps的速度送入到計(jì)算機(jī)。

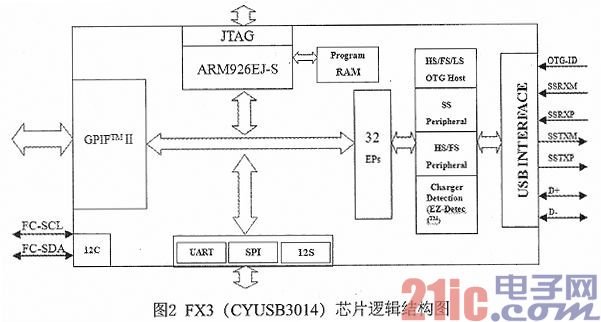

美國(guó)的賽普拉斯(CYPRESS)公司開發(fā)的EZUSB FX系列芯片以其強(qiáng)大的功能,簡(jiǎn)易的開發(fā)過程而深受開發(fā)者喜愛。EZ—USB FX3(CYUSB3014)芯片是其最新的USB接口芯片,不僅完全符合USB3.0標(biāo)準(zhǔn),而且還可以與DSP、FPGA、CPLD和單片機(jī)等處理器方便地相連,從而簡(jiǎn)化了系統(tǒng)的設(shè)計(jì)。EZ-USB FX3芯片內(nèi)部邏輯結(jié)構(gòu)如圖2所示。

CYUSB3014的內(nèi)核為一個(gè)200MHz工作頻率的32位ARM926EJ處理器,其通過固件程序和內(nèi)部DMA通道管理USB和GPIF II、I2S、SPI、UART接口之間的數(shù)據(jù)傳輸。CYUSB3014內(nèi)部有一個(gè)能實(shí)現(xiàn)5Gbps傳輸速度的GPIF II接口,該接口可以方便地與MAX 7000A連接。GPIF II接口不僅工作頻率可達(dá)100MHz,而且其數(shù)據(jù)總線可以根據(jù)需要選擇8位、16位和32位中的任何一種。當(dāng)然,只有選用了32位的數(shù)據(jù)總線,才能充分挖掘其帶寬。

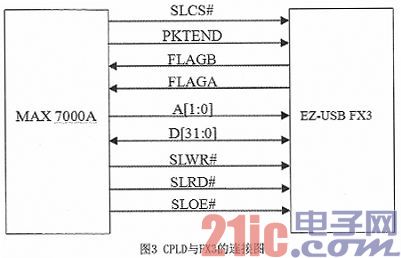

美國(guó)硅谷的Altera公司一直是創(chuàng)新定制邏輯解決方案的領(lǐng)先者,其開發(fā)了業(yè)界最先進(jìn)的FPGA、CPLD和ASIC技術(shù),其開發(fā)的MAX系列CPLD芯片深受開發(fā)者喜愛。只有采用高速的CPLD主控芯片才能充分發(fā)揮USB3.0的5Gbps超寬帶寬,為此Altera公司最新高速的MAX7000A系列CPLD為理想之選,我們采用了型號(hào)為MAX7128AETC100—4的主控芯片,該芯片的詳細(xì)資料見文獻(xiàn)。該芯片主要負(fù)責(zé)與GPIF II接口相連,實(shí)現(xiàn)GPIF II接口工作在SLAVEFIFO模式下向計(jì)算機(jī)寫入數(shù)據(jù)的邏輯時(shí)序控制。EZ—USB FX3的GPIF II接口有HOST主機(jī)和SLAV EFIFO兩種工作模式,本系統(tǒng)選用SLAVE FIFO工作模式,其與CPLD連接的原理圖如圖3所示。

系統(tǒng)工作原理如下:1)A[1:0]為地址選擇位,MAX7000A根據(jù)其值選擇對(duì)應(yīng)的Socket;2)D[31:0]為32位的傳輸數(shù)據(jù)總線,MAX7000A將需要寫入的數(shù)據(jù)放置在此總線上;3)SLCS為片選芯片,工作時(shí)需為低電平來選中EZ-USB FX3芯片;4)PKTEND為包結(jié)束信號(hào),當(dāng)數(shù)據(jù)包寫滿時(shí),該信號(hào)有效時(shí),MAX7000A將其打包傳送至EZ—USB FX3芯片;5)FLAGA和FLAGB為EZ—USB FX3返回給MAX 7000A的狀態(tài)標(biāo)志信號(hào),MAX7000A據(jù)此決定是否對(duì)EZ—USB FX3進(jìn)行數(shù)據(jù)讀寫;6)SLWR為寫使能信號(hào),SLRD為讀使能信號(hào),SLOE為輸出使能信號(hào)。

系統(tǒng)硬件設(shè)計(jì)中還包含了電源電路、USB接口電路和時(shí)鐘復(fù)位電路等電路的設(shè)計(jì),由于篇幅的關(guān)系,在此不作介紹。

2 系統(tǒng)軟件設(shè)計(jì)

系統(tǒng)軟件的開發(fā)包含了MAX 7000A CPLD和EZ—USB FX3的固件程序開發(fā)、EZ—USB FX3的Windows驅(qū)動(dòng)程序開發(fā)和上位機(jī)應(yīng)用程序的開發(fā)。我們利用CYPRESS公司提供的開發(fā)包,大大縮短了開發(fā)周期,提高了開發(fā)效率。

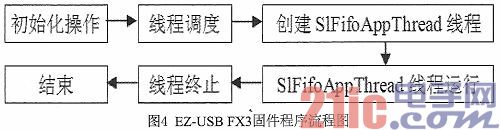

固件程序是微控制器系統(tǒng)的核心,是幫助設(shè)備實(shí)現(xiàn)相應(yīng)的功能。MAX 7000A CPLD固件程序主要完成對(duì)A/D芯片的控制和對(duì)EZ—USB FX3芯片的通信,其將A/D芯片采集的數(shù)據(jù)傳送給EZ—USB FX3。MAX 7000A CPLD的固件開發(fā)比較簡(jiǎn)單,只需對(duì)相應(yīng)的引腳和時(shí)序進(jìn)行定義。為此我們采用了Verilog HDL語言編寫,開發(fā)環(huán)境為Quartos II 8.0。EZ—USBFX3固件程序的主要功能是讓其將MAX 7000A CPLD芯片傳來的數(shù)據(jù)傳輸?shù)缴衔粰C(jī),實(shí)現(xiàn)超高速數(shù)據(jù)傳輸。EZ—USB FX3的控制器是基于ARM926EJS的,固件程序采用ECLIPSE集成開發(fā)環(huán)境,開發(fā)人員需在CYPRESS公司官網(wǎng)上下載其SDK安裝包。EZ—USB FX3的固件程序流程圖如下:

S1FifoAppThread線程代表著EZ—USB FX3芯片的GPIF II接口工作在SLAVE FIFO模式。我們需在S1FifoAppThread線程中定義一個(gè)DMA傳輸通道,此DMA通道在外部MAX 7000A芯片的控制下,將數(shù)據(jù)送至指定的輸入端點(diǎn),以供上位機(jī)應(yīng)用程序獲取。

在驅(qū)動(dòng)程序開發(fā)方面,CYPRESS公司的SDK為EZ-USB FX3提供了通用設(shè)備驅(qū)動(dòng)程序CYUSB3.SYS,其不僅完全符合WDF(Windows Driver Foundation)規(guī)范,還具有兼容USB2.0和USB3.0設(shè)備、支持即插即用和支持高帶寬數(shù)據(jù)傳輸?shù)葍?yōu)點(diǎn)。我們只需根據(jù)固件程序中定義的USB設(shè)備的VID和PID對(duì)通用驅(qū)動(dòng)程序相匹配的CYUSB3.INF文件進(jìn)行相應(yīng)的簡(jiǎn)單修改即可。

在上位機(jī)的應(yīng)用程序的開發(fā)方面,CYPRESS公司同樣為用戶提供了一個(gè)個(gè)操作簡(jiǎn)單、功能強(qiáng)大的C++編程接口:CyAPI.Lib庫函數(shù)。我們選用了Microsoft Visual Studio2008作為開發(fā)工具,通過CyAPI.Lib函數(shù)與CYUSB3.SYS設(shè)備驅(qū)動(dòng)程序傳遞數(shù)據(jù),進(jìn)行實(shí)時(shí)采集。

3 總結(jié)

本文詳細(xì)介紹了采用EZ—USB FX3為接口USB3.0芯片,MAX 7000A為主控芯片,設(shè)計(jì)與開發(fā)了一套USB 3.0數(shù)據(jù)采集傳輸系統(tǒng)。CYPRESS公司為EZ-USB FX3提供了完整的SDK開發(fā)包,縮短了開發(fā)周期。當(dāng)采樣數(shù)據(jù)為32位,采樣時(shí)鐘為40MHz時(shí),系統(tǒng)理論傳輸帶寬可達(dá)1.28Gps。實(shí)際測(cè)試中我們采用了16位的A/D高速芯片,MAX 7000A芯片工作時(shí)鐘為40MHz,實(shí)驗(yàn)測(cè)得系統(tǒng)傳輸速率約600Mbps,超過了USB2.0的480Mbps理論帶寬,這表明USB3.0總線能將采集的信號(hào)實(shí)時(shí)傳輸至計(jì)算機(jī),充分發(fā)揮了USB3.0超高速傳輸帶寬的優(yōu)勢(shì)。

評(píng)論