基于FPGA實現塔康地面信標信號發生器設計

摘要:為滿足某型飛機塔康設備檢測儀器要求,對其提供穩定、可靠、多樣的塔康地面信標信號。設計利用Altera公司的 EP4CE6E22C8為控制核心,以DAC813JP為DA轉換器,運用DDS基本原理,通過QuartusII軟件編寫塔康地面信標信號發生器的每個單元模塊,最終完成整個設計方案。并進行了Matlab與QuartusII相結合的仿真驗證,同時設計連接了外部電路。相較于傳統塔康地面信標信號發生器操作簡單,便于升級,能夠滿足檢測儀器的各項要求。

本文引用地址:http://www.104case.com/article/201609/303577.htm關鍵詞:塔康信號;直接數字頻率合成;現場可編程門陣列;數模轉換器

塔康(TACAN)是戰術空中導航系統的簡稱,是美國1955年研制并投入裝備的近程無線電導航系統,是一種測角測距系統。“塔康”系統,又稱作極坐標系統,能利用一個射頻通道同時傳遞距離與方位信息,從而簡化了機載設備,同時減少了對頻段的占用。該系統可供飛機的出航、歸航以及圓周飛行等航線飛行時使用,且在我軍各類飛機上大量裝備,因此設計塔康地面信標模擬器,用于檢測機載塔康設備具有重要作用。由于FPGA具有快速、靈活控制、設計周期短,同時 DDS具有高分辨率,實現方法靈活的特點,所以本文研究了FPCA內嵌DDS技術實現塔康方位信號發生器的解決方案。

1 基本原理

1.1 塔康信號

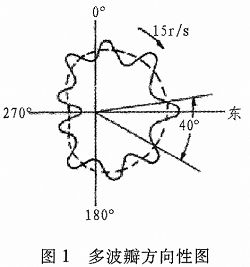

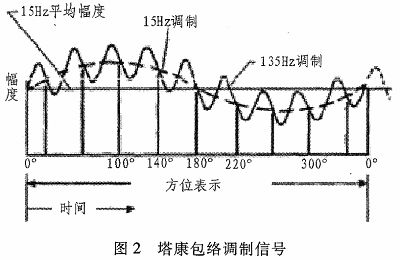

TACAN系統由塔康地面設備(塔康信標臺)和機載設備兩部分構成。該系統使用的是脈沖調制技術,并且它使用極坐標的方式來表示距離和方位。其中,系統通過天線的旋轉產生一個旋轉的多波瓣方向性圖來獲取方位,并且能夠提供粗、精方位信息。如圖1。塔康信號是由塔康地面信標臺以15 Hz和135 Hz復合調制的旋轉場向空中發射脈沖,形成15Hz和135 Hz脈沖包絡調制信號,這些信號包括方位基準信號和方位包絡信號,基準信號用脈沖編碼來識別,包絡信號則是利用脈沖序列幅度的方式來進行傳送。其表達式為:

Q(t)=A0+A1sin(2πft)+A2sin(9×2πft) (1)

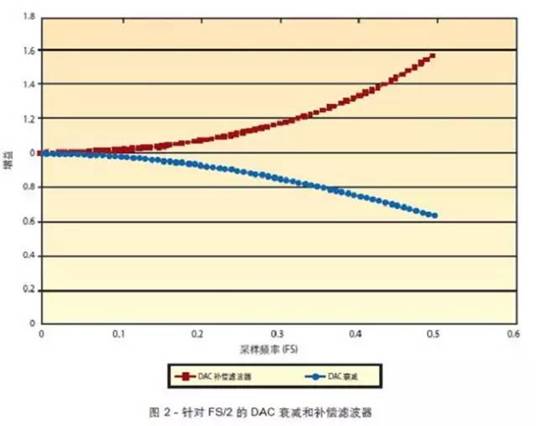

式中:f=15 Hz,A0為直流分量,A1、A2分別為大包絡、小包絡的調制幅度。經過調制后的信號就攜帶方位信息。在測量方位時,機載設備跟蹤主、輔基準脈沖,計算出基準與包絡相位零點之間的相位差,便可以完成定位工作。其調制信號如圖2所示。

1.2 包絡調制信號產生方案

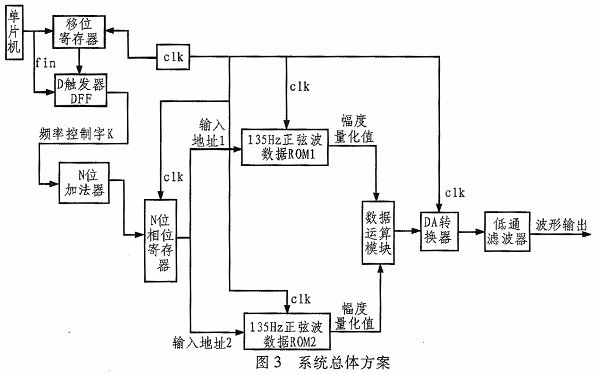

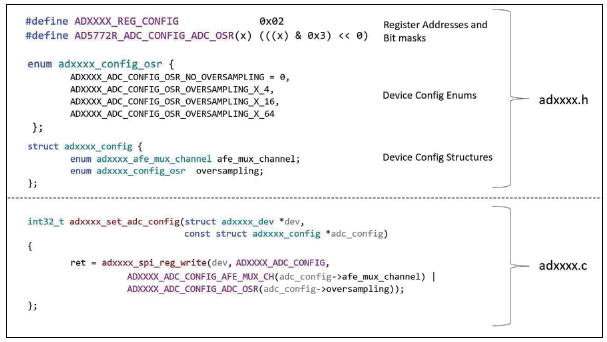

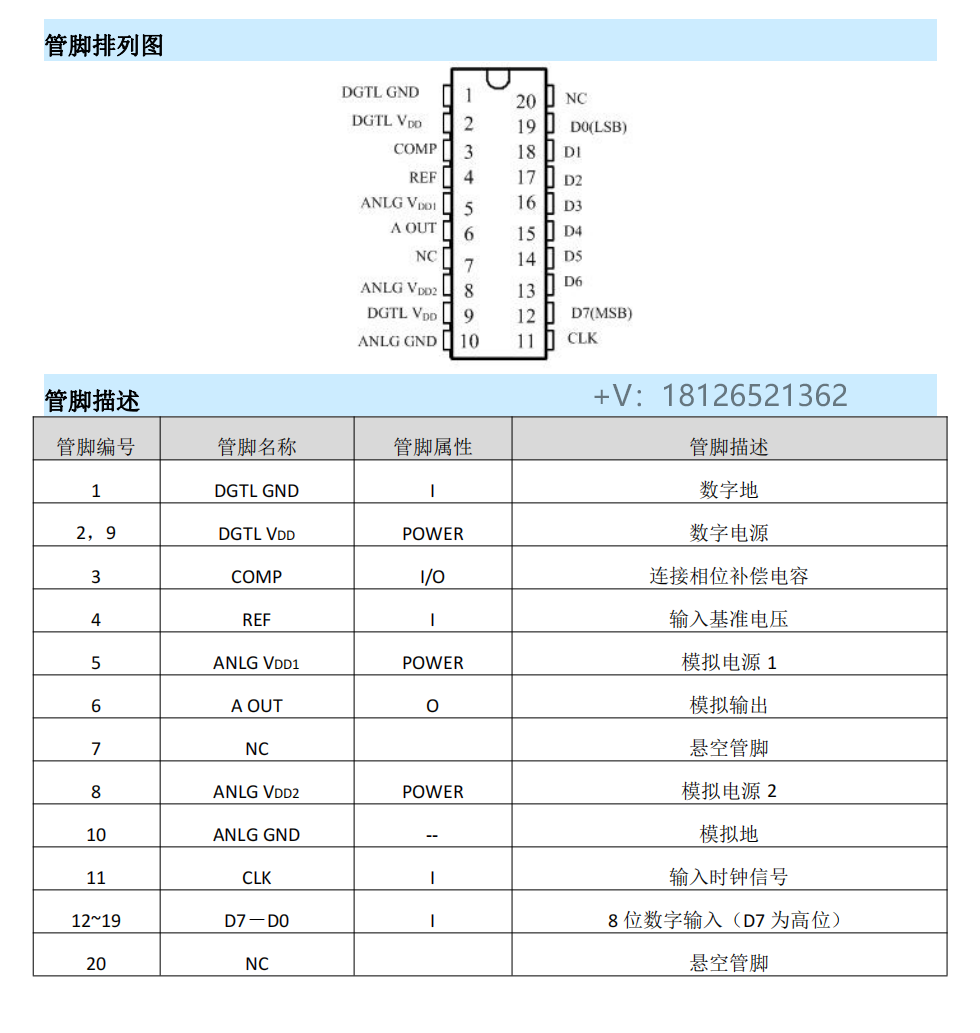

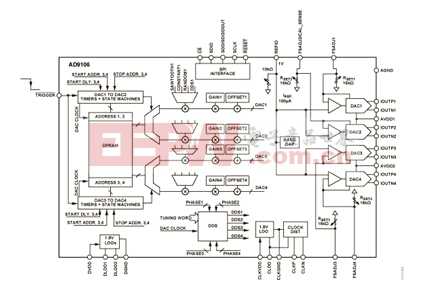

塔康信號外包絡是由15 Hz和135 Hz正弦波疊加后形成的波形。因為該信號頻率不高,本設計將輸出的數字幅度值通過DAC芯片及調理電路轉換為所需要的包絡信號。本設計中信號通過在 FPGA內部應用DDS技術來產生,使用VHDL語言編寫相位累加器、正弦波數據ROM,從而實現直接數字頻率合成。最后將數字信號送到數模轉換器 DAC,由DAC輸出所需要的波形。塔康信號的AM調制包絡是由15 Hz和135 Hz正弦波疊加而成。通過FPGA應用DDS技術,產生兩路正弦波疊加后對應的幅度量化值,然后將波形數據送到數模轉換器DAC 813JP轉換為模擬波形,最后通過低通濾波器濾波送到調制電路使用。

2 系統方案設計

方案以Altera公司的Cyclone系列的EP1C12Q240C8芯片為核心,以QuartusII為軟件平臺,以FPGA開發板為硬件平臺,在FPGA內部編寫不同的功能模塊,加上外擴的DA轉換器和低通濾波器,完成塔康信號發生器的設計。其總體方案如圖3所示。

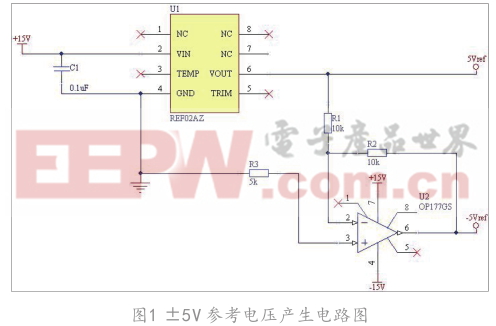

2.1 系統外部電路設計

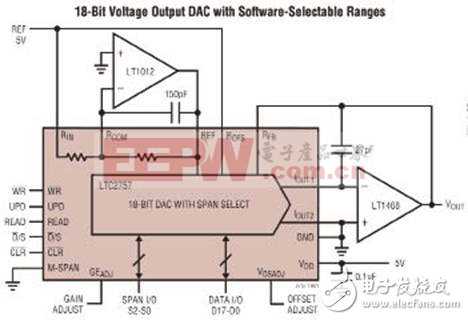

通過單片機為信號發生器提供信號所需要的參數以便滿足檢測儀不同的要求。數模轉換器是數字電路和模擬電路連接的橋梁,FPGA輸出的波形數據用DAC813JP進行D/A轉換,然后輸出信號經過I/V轉換后,通過低通濾波器輸出。本設計采用巴特沃茲二階濾波器濾波。

外部電路的具體設計在此就不再贅述。

2.2 系統軟件功能實現

本設計的實現軟件功能的模塊主要分為3個單元。首先用VHDL語言在軟件平臺QuartusII中編寫每個單元并生成原理圖,然后在頂層模塊文件中將每個單元原理圖連接起來,最后配置引腳并進行編譯,從而完成整個軟件部分的設計。

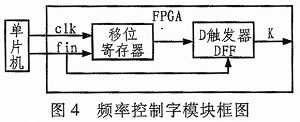

2.2.1 頻率控制字模塊

頻率控制字K是二進制的相位增量值,它控制著最后輸出波形頻率的大小。作為相位累加器的輸入,它的好壞直接影響整個系統的功能和性能。為產生所需要的頻率控制字K,單片機輸入的控制量通過串行外圍設備接口與FPGA進行通信。其流程框圖如圖4所示。

2.2.2 相位累加器模塊

相位累加器是FPGA邏輯控制的核心部分,一般由加法器和同步寄存器構成,實現相位累加。相位增量△φ=2π/2N對應的二進制表示為A△φ,即頻率控制字K。K與輸出頻率f0呈簡單的線性關系:

因此只要對相位的量化值進行累加,即可得到當前信號的向未知。在參考時鐘的作用下,相位累加器進行線性的相位累加,當累加器溢出時即完成一個周期性動作,系統完成一個周期的頻率合成信號,累加器的溢出頻率就是系統輸出的信號頻率。

本設計采用3級流水線設計,與普通相位累加器相比,雖然延時了兩個時鐘周期才輸出結果,但是結果沒有發生任何改變,反而大大提高了相位累加器的計算速率。

2.2.3 波形數據ROM模塊

相位累加器的輸出值即為波形數據ROM的查詢地址,通過ROM進行相位-幅度的轉換,就可以在給定的時間上確定波形的抽樣幅值。ROM模塊直接由QuartusII中MegaWizard Plug—in Manager工具產生。要產生ROM模塊,需要.mif文件。可以利用Matlab產生.mif文件,但是其產生的.mif文件不可以直接使用,需要添加程序:

評論