嵌入式高速圖像數據采集板設計方案

本文提出了一種基于FPGA+ARM的高速數據采集板的設計方案。該方案采用FPGA完成高速數據采集,通過ARM對FPGA進行控制管理。利用 DMA技術實現了FPGA與ARM之間的數據采集接口設計方案,并實現了Linux操作系統下FPGA設備的中斷處理程序的開發。并通過設計千兆以太網接口實現了圖像數據的實時遠程傳輸。

本文引用地址:http://www.104case.com/article/201609/303375.htm1.概述

隨著圖像處理技術的快速發展,圖像采集處理系統在提高工業生產自動化程度中的應用越來越廣泛。本文結合實際系統中的前端圖像處理和圖像數據傳輸的需要,充分利用ARM的靈活性和FPGA的并行性的特點,設計了一種基于ARM+FPGA的高速圖像數據采集傳輸系統。所選用的ARM體系結構是32位嵌入式RISC微處理器結構,該微處理器擁有豐富的指令集且編程靈活;而FPGA則在速度和并行運算方面有很大優勢,適合圖像處理的實時性要求;并且通過千兆以太網接口實現了采集板與上位機之間圖像數據的高速遠程傳輸。

2.硬件設計方案

2.1 系統總體設計

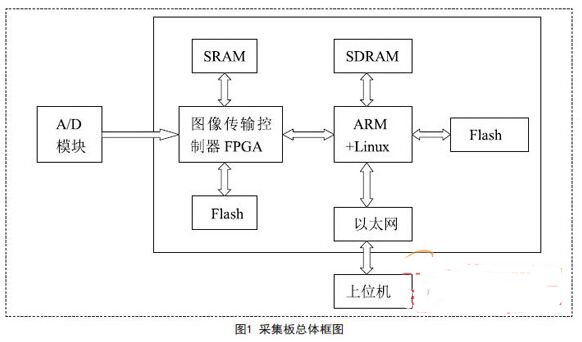

本設計采用的ARM芯片為三星公司的S3C2440A、FPGA芯片為Xilinx公司生產的Spartan系列的S3C500E芯片,系統組成還包括千兆以太網控制芯片AX88180、千兆PHY芯片88E1111、存儲器、嵌入式Linux、網絡驅動程序等(如圖1所示)。

本設計的主控芯片S3C2440A是基于ARM920T核的16/32位RISC微處理器,采用了0.13um的CMOS標準宏單元和存儲器單元,運行頻率高達500MHz.ARM920T 實現了MMU,AMBA BUS和Harvard高速緩沖體系結構構。這一結構具有獨立的16KB指令Cache和16KB數據Cache.每個都是由具有8字長的行組成。通過提供一套完整的通用系統外設,S3C2440A減少整體系統成本和無需配置額外的組件。它主要面向手持設備以及高性價比、低功耗的應用,具有非常豐富的片上資源。

FPGA芯片S3C500E主要用于圖像傳感器的控制、圖像數據的緩存及外圍芯片時序的產生。它通過控制A/D實現數據采集,并保存至SRAM,對ARM的讀寫信號進行譯碼以將目標數據讀回ARM并傳到上位機。

ARM芯片S3C2440A負責整個系統的控制,它通過讀寫總線上的地址來進行指令和數據的傳輸以控制FPGA的所有動作[1-2].嵌入式Linux內核負責系統任務的管理并集成TCP/IP協議,方便實現網絡控制功能。

S3C2440A與AX88180以總線方式連接,是通信控制的主體。S3C2440A通過網絡驅動程序實現對AX88180內部寄存器編程,以及對以太網數據的發送和接收,從而完成網絡與系統之間的數據傳輸。

AX88180與88E1111之間采用RGMII接口方式互連,負責數據傳送底層協議的實現。

2.2 數據采集接口設計

系統設計的難點在于數據采集接口的設計,它是數據傳輸的通道,同時也是連接系統前后端的橋梁。本系統采用S3C2440A和S3C500E配合共同實現數據的高速采集。

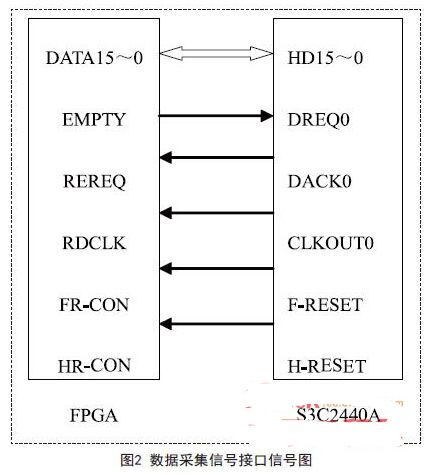

直接內存存取(DMA)作為一種獨立于CPU的后臺批量數據傳輸技術,以其快速、高效的特點在數據采集領域得到了廣泛的應用。本設計中,S3C2440A采用外部DMA方式采集FPGA內部存儲數據,其接口信號連接如圖2所示。

接口設計的FPGA部分主要包括異步FIFO模塊、復位模塊和數據緩沖模塊組成.異步FIFO模塊主要解決圖像輸出數據頻率和數據采集的頻率不匹配的問題,系統采用的異步FIFO寬度為8bits,深度為2048.復位模塊在控制信號的作用下實現對系統的FIFO的復位控制。

系統采用DMA通道0采集圖像數據。

其中,DREQ0和DACK0分別為DMA的請求和應答信號。FPGA的空信號EMPTY與DREQ0相連,讀請求RDREQ與DACK0相連。 FPGA寫時鐘由圖像輸出位同步信號提供,讀時鐘由S3C2440A的時鐘輸出引腳CLKOUT0提供。CLKOUT0根據S3C2440A內部寄存器的設置可以輸出幾種不同的時鐘頻率。FIFO的讀操作與ARM的DMA操作配合進行。系統采用單服務命令模式的DMA操作,每次傳輸一個字節數據位。當 DREQ0信號變為低電平時DMA操作開始,每次傳輸一個字節后產生一個DACK0應答信號,而且只要DREQ0為低電平DMA操作就繼續進行,直到 DMA控制寄存器中的計數器為0,產生DMA中斷。根據上述時序特點,將FIFO的空信號作為DMA的請求信號DREQ0.當圖像輸出的數據寫入FIFO 中時,空信號跳變為低電平啟動DMA操作,同時以DACK0信號作為FIFO的讀請求。每次DMA操作后產生的應答信號DACK0使FIFO內部的讀指針前移1位指向下次要讀出的數據。F-RESET和H-RESET分別控制FPGA內的幀同步復位和行同步復位,保證系統在每幀信號到來時開始工作,同時每采集完一行信號復位FIFO.FIFO輸出數據經過以nGCS4為選通信號的BUFFER后接到ARM的數據總線上。nGCS4是S3C2440A存儲空間中BANK4的片選信號,當S3C2440A對地址范圍0×20000000~0×28000000的存儲空間進行讀寫操作時為低電平,其余時間為高電平,NGCS4作為緩沖模塊的選通信號可以有效地避免數據總線的污染。

2.3 網絡傳輸接口設計

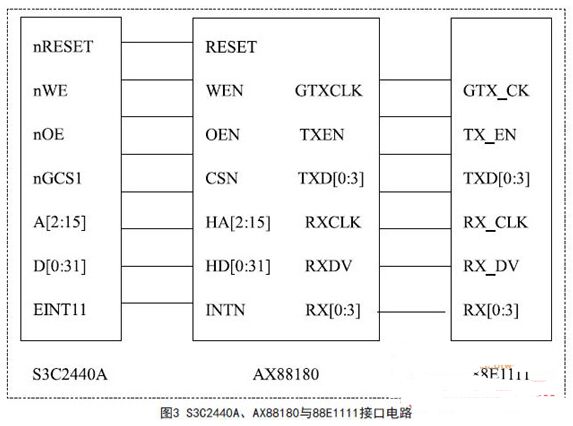

本設計采用的以太網控制器為臺灣亞信公司推出的一款Non-PCI千兆以太網控制芯片AX88180.其內置1000Mbps以太網媒體存取控制器(MAC);它可以十分方便地實現與一般16/32位微處理器連接,并且可以像SRAM一樣被訪問;它有40KBytesSRAM網絡封包緩存器。它符合 IEEE802.3/IEEE802.3u/IEEE802.3ab協議,可廣泛應用于各種消費電子和家庭網絡市場或要求更高的網絡帶寬連接,如數字媒體、家用網關及IP電視等。

嵌入式芯片S3C2440A、以太網控制器AX88180及物理層芯片88E1111的接口電路圖如圖3所示。

S3C2440A與AX88180之間采用總線方式相連,地址總線A2~A15、數據總線D0~D31、讀寫信號等可以直接連接,AX88180中斷信號與S3C2440A EINT11相連,AX88180的40M~100M時鐘信號由S3C2440A提供,整個接口電路無需外加電路;AX88180與PHY芯片之間采用簡化千兆比特媒體RGMII接口,信號對應 相連,負責實現數據傳送底層協議[5].

評論