基于高速串行接口的雷達信號采集回放系統(tǒng)

摘要:針對雷達現(xiàn)場中復雜多變的電磁信號難以及時分析處理,本文提出了一種基于高速串行接口的雷達中頻信號采集回放系統(tǒng)。該系統(tǒng)充分利用JESD204B高速串行接口和吉比特收發(fā)器,通過Xilinx Virtex FPGA芯片對其進行控制,實現(xiàn)雷達中頻信號的高速、高精度、可靠、穩(wěn)定采集和回放,有效地解決了高速數(shù)據(jù)流并行傳輸時存在碼間串擾的問題。

本文引用地址:http://www.104case.com/article/201605/291774.htm背景

雷達現(xiàn)場環(huán)境中的電磁信號不僅包含了目標信息,還包含了電子干擾、天氣、地形等豐富的信息,其信號數(shù)量龐大和信號種類多樣的特點致使后期難以及時實現(xiàn)高速數(shù)據(jù)流的處理和分析。因此,如何實現(xiàn)雷達現(xiàn)場信號的高速采集和重現(xiàn)是現(xiàn)今討論尤為激烈的話題之一。同時,這對雷達外場試驗、演習數(shù)據(jù)分析、雷達檢修和部隊訓練都有著重要的現(xiàn)實意義。

在現(xiàn)代雷達信號處理系統(tǒng)的研制中,一般需要對中頻雷達信號進行高速度和高精度采集。目前使用的并行采樣傳輸模式雖然可以實現(xiàn)此要求,但是隨著采集速率的提高,并行數(shù)據(jù)之間的誤碼率也在成倍增加[1]。本文采用帶有高速串行接口JESD204B的模數(shù)轉(zhuǎn)換芯片實現(xiàn)多路雷達中頻信號的高速度、高精度采集,以Xilinx Virtex-6配備的多路吉比特收發(fā)器進行采集數(shù)據(jù)流的可靠穩(wěn)定傳輸,并使用可進行4倍插值的數(shù)模轉(zhuǎn)換芯片實現(xiàn)高速信號的高精度模擬轉(zhuǎn)換。FPGA作為該系統(tǒng)的主控,不僅完成了各器件的配置,而且實現(xiàn)了采集和回放過程的數(shù)據(jù)信道化,使得系統(tǒng)更完整,通用性更強。

1 系統(tǒng)框圖

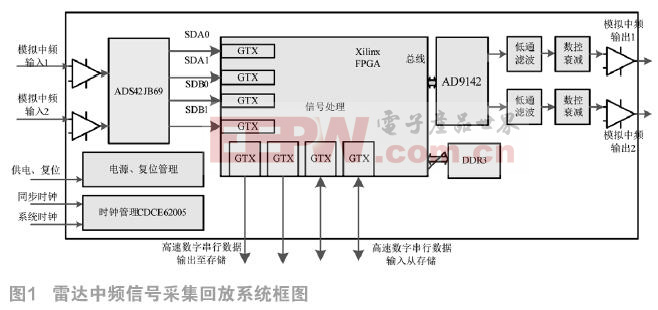

該雷達中頻采集回放系統(tǒng)設計如圖1所示。該系統(tǒng)主要包括四個模塊:A/D模塊、D/A模塊、信號處理模塊和時鐘復位管理模塊。ADC模塊主要是通過ADS42JB69實現(xiàn)雙通道16位250MSPS高速采樣,其前端可由兩路放大器及變壓器對中頻模擬信號進行調(diào)理,使之符合ADC芯片射頻輸入端口的要求;DAC模塊主要由AD9142芯片、低通濾波器、數(shù)控衰減器和放大器組成,通過對DAC芯片進行4倍插值可以實現(xiàn)16位高達1000MSPS的數(shù)模轉(zhuǎn)換;信號處理采用XC6VLX240TFF1156芯片對各模塊進行管理并實現(xiàn)數(shù)據(jù)的信道化處理;時鐘復位管理模塊包括圖1中所示的電源、復位管理和時鐘管理,其主要功能是為系統(tǒng)中的其它模塊提供供電、時鐘和復位等。

2 高速串行接口

2.1 JESD204B

JESD204B 協(xié)議體系結(jié)構(gòu)可分為物理層、鏈路層、傳輸層和應用層。物理層實現(xiàn)高速數(shù)據(jù)串/并行轉(zhuǎn)換、并/串行轉(zhuǎn)換以及編碼處理;鏈路層負責編碼幀數(shù)據(jù)、校驗數(shù)據(jù)、添加幀的邊界和流量控制,過程中只發(fā)送和接收幀而無需知道幀的內(nèi)容[2];傳輸層則是將AD采樣信息從數(shù)據(jù)流中提取出來。JESD204B接口由接收器和電流模式邏輯(CML)驅(qū)動器的差分對組成,共模擬電平范圍為0.72V~1.23V,通信速率可低至312.5Mbps,可高達3.125Gbps[3]。相比于其它接口,它不僅實現(xiàn)了高速數(shù)據(jù)的可靠穩(wěn)定傳輸,而且在硬件上減少了管腳數(shù)量,簡化了ADC和FPGA的布線,特別是對于多片ADC的系統(tǒng)。JESD204B接口的這一特性使其擁有廣闊的應用前景。

2.2 GTX

Virtex-6 FPGA是Xilinx公司推出的一塊高性能低功耗FPGA[3]芯片。本文選用XC6VLX240TFF1156芯片,該芯片內(nèi)嵌5個Quard,每個Quard包含4個千兆位收發(fā)器GTX,每個GTX收發(fā)器都集成了發(fā)射器和接收器功能,能以480MB/s~6.6GB/s的速率運行,且其有大量可配置的用戶定義特性和參數(shù)[4]。其結(jié)構(gòu)由物理媒介適配層PMA(Physical Media Access)和物理編碼子層PCS(Physial Code Subplayer)兩部分組成。PCS提供豐富的物理編碼層特性,包括周期冗余檢測CRC(Cyclic Redundancy Check)、8B/10B編碼、發(fā)送FIFO、8B/10B解碼及用于通道綁定和時鐘校準的彈性緩沖器等模塊;PMA部分為模擬電路,提供高性能的串行接口特性,如預加重和均衡等功能,主要包括串行轉(zhuǎn)換、差分接收器、并串轉(zhuǎn)換及時鐘數(shù)據(jù)恢復(CDR)等模塊[5]。

對于GTX的時鐘可以選擇外部供給,而且相鄰的Quard可以使用同一對差分時鐘。發(fā)送端用戶時鐘TXUSRCLK2是由TXOUTCLK驅(qū)動,接收端用戶時鐘RXUSRCLK2是由RXRECCLK驅(qū)動,即是從接收到的數(shù)據(jù)里恢復出來的時鐘[6]。要注意發(fā)送端還有另外一個用戶時鐘TXUSRCLK是PCS內(nèi)部邏輯時鐘,不允許用戶直接使用,接受端的RXUSRCLK類似,其速率為線速率與數(shù)據(jù)位寬之比。

GTX接口眾多特性使其能夠方便地實現(xiàn)PCIE、SATA、SAS等高速串行接口的物理層與鏈路層橋接。本文使用GTX接口實現(xiàn)JESD204B協(xié)議,以正確解析JESD204B接口ADC轉(zhuǎn)化器發(fā)出的數(shù)據(jù)。

3 信號處理

3.1 A/D

基于JESD204B標準設備與FPGA內(nèi)嵌的吉比特收發(fā)器可實現(xiàn)完美對接,該系統(tǒng)選用TI公司生產(chǎn)的ADS42JB69作為A/D轉(zhuǎn)換的主要器件。它是一款高線性、雙通道、16位、250MSPS的模數(shù)轉(zhuǎn)換器,支持JESD204B串口,數(shù)據(jù)速率高達3.125Gbps。經(jīng)緩沖的模擬輸入在大大降低采樣保持毛刺脈沖能量的同時,在寬頻率范圍內(nèi)提供統(tǒng)一的輸入阻抗,這使得它可以輕松地將模擬輸入驅(qū)動至極高輸入頻率[7]。采樣時鐘分頻器可實現(xiàn)更靈活的系統(tǒng)時鐘架構(gòu)設計。此期間采用內(nèi)部抖動算法以在寬輸入頻率范圍內(nèi)提供出色的無雜散動態(tài)范圍(SFDR)。

ADS42JB69首先根據(jù)需要完成數(shù)據(jù)采集,然后通過JESD204B接口將采集的并行數(shù)據(jù)送至FPGA。根據(jù)模數(shù)轉(zhuǎn)換的最大速率,JESD204B可配置成兩種工作模式:四線模式和兩線模式。本文假定ADC的采樣速率為250MSPS,那么JESD204B接口就必須工作在四線模式,即DA0和DA1分別對應A通道的高低8位,B通道同理。其中, 端口用來控制串行端口輸出的數(shù)據(jù)類型,其可作為多片ADC采集的同步控制。此外,還可通過SPI對ADC芯片的寄存器0x0f進行配置,實現(xiàn)除了正常工作模式外的多種測試模式,如遞增碼、隨機碼、零一交錯碼等。JESD204B完成數(shù)據(jù)傳輸要經(jīng)過兩步:編碼以及串并轉(zhuǎn)換。本文使用8B/10B編碼,結(jié)合A/D轉(zhuǎn)換速率,發(fā)送端的線速率就是;如果采用雙通道進行采集,那么總的數(shù)據(jù)量就是。

在串行數(shù)據(jù)收發(fā)過程中如何界定數(shù)據(jù)的邊界是至關重要的。JESD204B協(xié)議采用插入控制字符以完成字同步和幀同步來確定數(shù)據(jù)的邊界,結(jié)合接收端對端口的控制,可實現(xiàn)采集數(shù)據(jù)的準確和可靠傳輸。本文對其控制實現(xiàn)可分為三步:

第一步:接收端拉低,發(fā)送端持續(xù)發(fā)送/K28.5/ 控制字。當接收端接收到4個/K28.5/字符后表明字同步建立完成,此時,接收端也已經(jīng)完成時鐘恢復以及Comma字符堅持測;

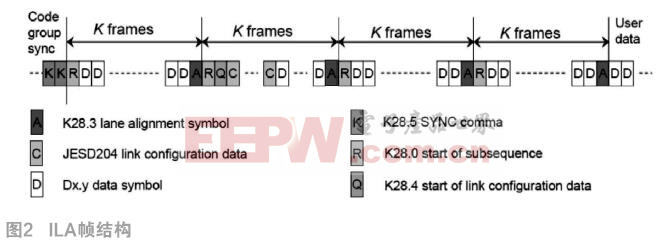

第二步:接收端拉高,發(fā)送端開始發(fā)送ILA幀。每個ILA包含4個多幀(Multi-Frame)。幀的結(jié)構(gòu)如圖2所示;

第三步:當接收端接收到ILA幀后就表明采集數(shù)據(jù)開始,其中可通過判斷/K28.3/字符的個數(shù)來確定起始有效數(shù)據(jù)。

3.2 D/A

進行數(shù)模轉(zhuǎn)換的關鍵是器件的選擇以及配置。本文選擇ADI公司生產(chǎn)的AD9142作為本系統(tǒng)的數(shù)模轉(zhuǎn)換芯片。AD9142是一款雙通道、16位、高動態(tài)范圍的數(shù)模轉(zhuǎn)換器,可通過插值實現(xiàn)最高1600MSPS的采樣速率,并可產(chǎn)生高達奈奎斯特頻率的多載波。它具有針對直接變頻傳輸應用進行優(yōu)化的特性,其中包括復數(shù)數(shù)字調(diào)制、輸入信號功率檢測以及增益、相位與失調(diào)補償。3線式串行接口允許對內(nèi)部寄存器進行編寫和回讀,是一款高性能、低噪聲的數(shù)模轉(zhuǎn)換芯片[8]。

如果要實現(xiàn)采集信號的實時回放,那么數(shù)據(jù)時鐘(DCI時鐘)就是250MSPS,SPI總線配置AD9142完成4倍插值就可實現(xiàn)高達1000MSPS的數(shù)模轉(zhuǎn)換。為確保AD9142實現(xiàn)可靠及高性能工作,其必須遵循一定的步驟,具體為(從器件上電后開始):

第一步:時鐘芯片CDCE62005提供穩(wěn)定的數(shù)模轉(zhuǎn)換DAC時鐘,項目中配置為1000MHz;

第二步:FPGA提供穩(wěn)定的數(shù)據(jù)同步DCI時鐘,項目中FPGA提供250MHz LVDS電平的差分時鐘;

第三步:SPI總線發(fā)出復位命令復位芯片,并配置其它相關參數(shù),如PLL、數(shù)據(jù)接口、插值濾波器、NCO、SINC等;

第四步:SPI總線配置完成后,提供穩(wěn)定的數(shù)據(jù)實現(xiàn)數(shù)模轉(zhuǎn)換。

3.3 信道化

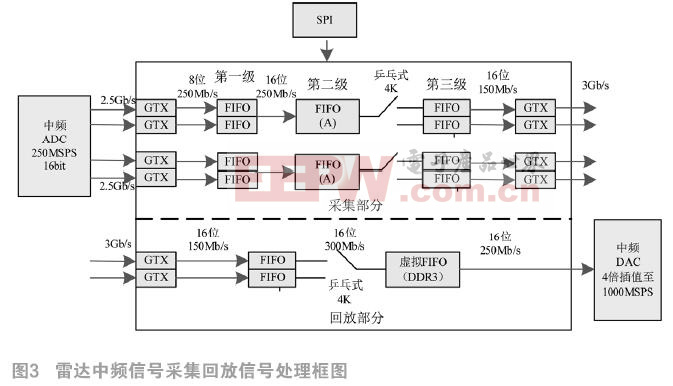

對于雷達中頻采集回放系統(tǒng),為了滿足后端存儲速率不定的要求,本文設計了基于FPGA的信道化處理框圖,增強了系統(tǒng)的通用性。

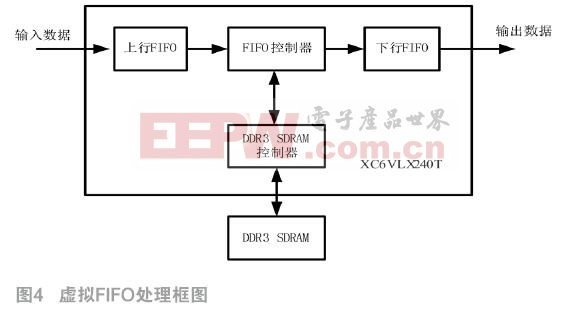

如圖3所示,對于采集部分,因為每路ADC都是以高低字節(jié)分開的方式傳輸數(shù)據(jù),因此要嚴格保證采樣時鐘同步,這在工程中很難實現(xiàn)。第一級FIFO設置存儲深度為32B,當FIFO中可讀數(shù)據(jù)達10個后,開始以同一個時鐘讀取FIFO,完成采樣數(shù)據(jù)高低字節(jié)的同步以及拼接;第二級FIFO作為數(shù)據(jù)緩存,深度設置為8KB,不僅杜絕了前端拼接后數(shù)據(jù)出現(xiàn)亞穩(wěn)定狀態(tài),而且為后續(xù)用戶邏輯提供簡單接口[9]。當FIFO可讀數(shù)據(jù)達到4KB時,READY信號拉高,開始向第三級FIFO寫入數(shù)據(jù);第三級FIFO除了作為乒乓式讀取上一級FIFO的緩存,還為后續(xù)GTX編碼爭取更多時間。三級FIFO聯(lián)合工作可實現(xiàn)告訴采集數(shù)據(jù)流的可靠穩(wěn)定傳輸[10]。

本文來源于中國科技期刊《電子產(chǎn)品世界》2016年第5期第73頁,歡迎您寫論文時引用,并注明出處。

評論