【E討論】關于邊沿檢測簡單理解

1、所謂邊沿檢測,就是檢測輸入信號或FPGA內部邏輯信號電平的跳變,即實現上升沿或下降沿的檢測,捕獲到以后以此用作使能信號(簡單可理解為:一旦檢測到這個信號,則發生什么什么),來作為時序邏輯的觸發信號。總之,在基礎中,這個還是很重要的,在后面的串口和SPI接口中都要用到。

本文引用地址:http://www.104case.com/article/201605/290591.htm(一)、一級寄存器

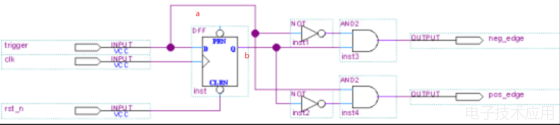

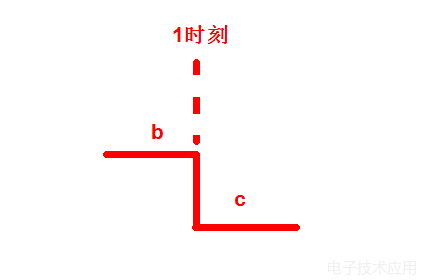

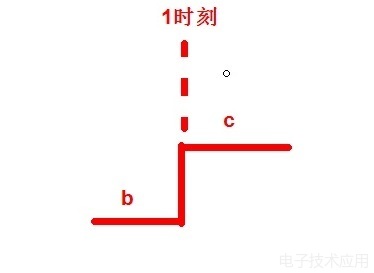

從一級寄存器中很好理解下降沿和上升沿的檢測:a和b都是從trigger來的(三者一樣),只是b比a在時間上遲了一個寄存器的時間。現在假設0時刻到了,trigger到a了,但是還沒有到b,到了寄存器,被寄存了;等待下一個時刻1到來,a走了(不用管了),來了一個新的叫c,同時,b從寄存器得到了之前寄存的,那個現在的1時刻,有了兩個信號,b和c,而且b是前一個時刻的,而c是現在時刻的(誰先誰后這點很重要)。所以:

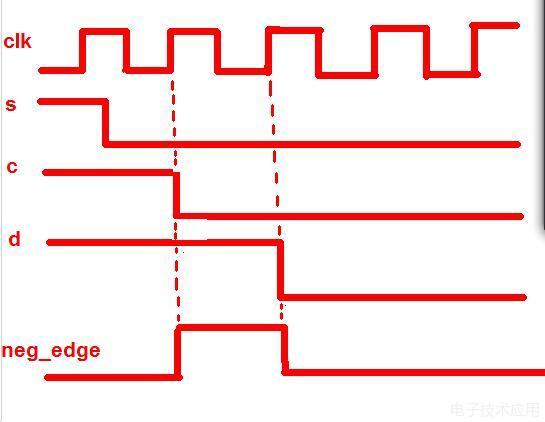

下降沿 neg_edge = b & ~c;

由上圖可以看出,當下降沿來的時候,c取反再與上b,得出輸出為1;反過來想,輸出neg_edge為1的時候就表示檢測到下降沿了。

上升沿 pos_edge = ~b & c;

同理。當pos_edge為1,表示檢測到上升沿。

(二)兩級寄存器

moduleedge_tech_design

(

clk,

rst_n,

s,

neg_edge,

pos_edge

);

inputclk;

inputrst_n;

inputs;

outputneg_edge;

outputpos_edge;

regc,d;

always@(posedgeclkornegedgerst_n)

if(!rst_n)begin

c<=1'b0;

d<=1'b0;

end

elsebegin

c<=s;

d<=c;

end

assignneg_edge=d&!c;

assignpos_edge=!d&c;

endmodule

為了在波形圖中能看到c、d寄存器,把程序修改為

moduleedge_tech_design

(

clk,

rst_n,

s,

neg_edge,

pos_edge,

c,//為了觀察c和d的波形而添加的

d//為了觀察c和d的波形而添加的

);

inputclk;

inputrst_n;

inputs;

outputneg_edge;

outputpos_edge;

outputc,d;//為了觀察c和d的波形而添加的

regc,d;

always@(posedgeclkornegedgerst_n)

if(!rst_n)begin

c<=1'b0;

d<=1'b0;

end

elsebegin

c<=s;

d<=c;

end

assignneg_edge=d&!c;

assignpos_edge=!d&c;

endmodule

測試文件如下:

`timescale1ns/1ns

`defineclk_period20

moduleedge_tech_design_tb;

regclk;

regrst_n;

regs;

wireneg_edge;

wirepos_edge;

wirec,d;//為了觀察c和d的波形而添加的

edge_tech_designedge_tech_design

(

.clk(clk),

.rst_n(rst_n),

.s(s),

.neg_edge(neg_edge),

.pos_edge(pos_edge),

.c(c),//為了觀察c和d的波形而添加的

.d(d)//為了觀察c和d的波形而添加的

);

initialclk=1;

always#(`clk_period/2)clk=~clk;

initialbegin

rst_n=1'b0;

s=1'b0;

#(`clk_period/4)

#(`clk_period)

rst_n=1'b1;

s=1'b1;

#(`clk_period*5)

s=1'b0;

#(`clk_period)

s=1'b1;

#(`clk_period)

s=1'b0;

#(`clk_period*3)

s=1'b1;

#(`clk_period)

s=1'b0;

#(`clk_period*5)

s=1'b1;

#(`clk_period)

s=1'b0;

#(`clk_period*3)

s=1'b1;

#(`clk_period)

s=1'b0;

#(`clk_period)

s=1'b1;

#(`clk_period*3)

s=1'b0;

#(`clk_period)

s=1'b1;

#(`clk_period)

s=1'b0;

#(`clk_period)

$stop;

end

endmodule

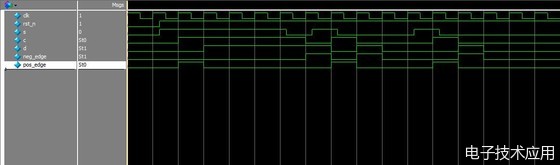

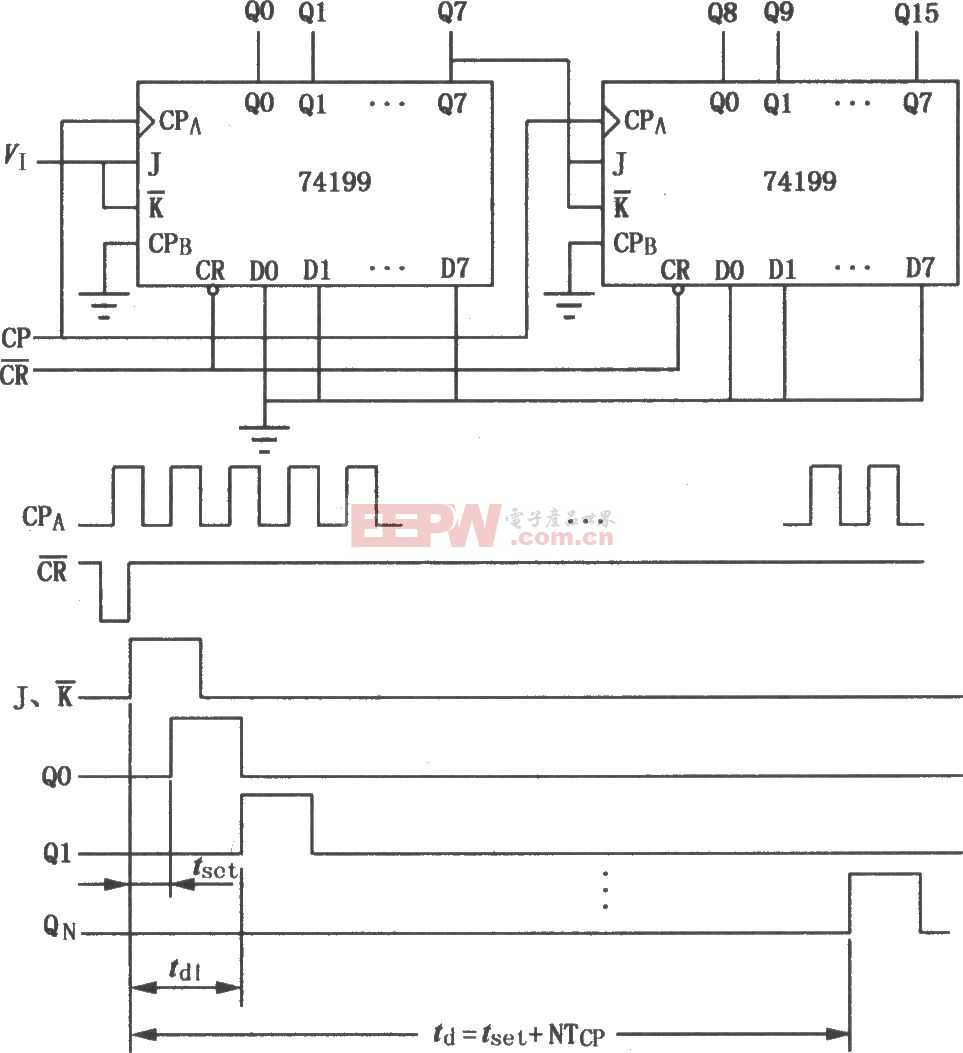

在仿真圖中可以看到這樣的圖形(街區圖中下降沿部分一小段)

輸入信號s從高變成低的時候,出現下降沿,然后等到時鐘clk的上升沿到來,s傳輸到c,d還沒傳輸到,被寄存在d之前的寄存器內,等待第二個時鐘上升沿到來,寄存器中的信號傳輸到d了,此時根據

neg_edge = d & ~c;

可以得到neg_edge的波形。

評論