遠(yuǎn)程心電醫(yī)療信號(hào)監(jiān)測(cè)系統(tǒng)設(shè)計(jì)

3.4 顯示模塊設(shè)計(jì)

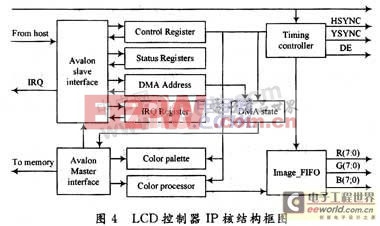

為了能夠直觀地顯示出采集的心電波形,需要顯示設(shè)備的支持。本設(shè)計(jì)采用的LCD面板是TFT 320*240 LCD。該LCD模塊沒(méi)有顯示控制器,因此需要設(shè)計(jì)顯示控制器IP核來(lái)驅(qū)動(dòng)LCD面板。本設(shè)計(jì)實(shí)現(xiàn)的顯示控制器IP核采用Verilog HDL設(shè)計(jì),支持多種顏色模式,包括18bpp,16bpp,8bpp和自定義模式。圖像存儲(chǔ)器lcd_fifo是采用片內(nèi)FIFO,可以根據(jù)需要進(jìn)行詞整。256色的顏色查找表采用片內(nèi)RAM來(lái)存儲(chǔ)。圖像信息能夠通過(guò)AvaIon總線主端口寫(xiě)入的突發(fā)塊傳輸方式進(jìn)行傳輸,利用DMA從內(nèi)存中自動(dòng)讀取,在SDRAM圖像存儲(chǔ)器image_ram與片上圖像數(shù)據(jù)緩存器lcd_fifo之間建立了一條專用DMA通道,該控制器結(jié)構(gòu)如圖4所示。

該LCD控制器IP核主要由4個(gè)模塊組成:接口模塊、內(nèi)存模塊、顏色轉(zhuǎn)換模塊和時(shí)序模塊。

接口模塊主要是NiosⅡ處理器對(duì)LCD控制器進(jìn)行控制及狀態(tài)讀取。接口模塊主要是以寄存器方式存在的,其中寄存器有:控制寄存器、狀態(tài)寄存器、DMA地址寄存器和中斷寄存器。

內(nèi)存模塊是Avalon總線的主接口部分,在系統(tǒng)啟動(dòng)之后,利用DMA傳輸模式,通過(guò)Avalon總線主端口寫(xiě)入的突發(fā)塊傳輸方式,完成圖像數(shù)據(jù)存儲(chǔ)器image_ram中的圖像數(shù)據(jù)到片上圖像數(shù)據(jù)緩存器lcd_fifo的獨(dú)立讀取。采用DAM傳輸方式是為了把NiosⅡ軟核處理器從頻繁地進(jìn)行數(shù)據(jù)讀取操作的工作中解脫出來(lái),這樣可以大大提高系統(tǒng)的工作效率。

顏色轉(zhuǎn)換模塊將讀取后的數(shù)據(jù)根據(jù)4種顏色模式不同進(jìn)行數(shù)據(jù)讀取的轉(zhuǎn)換,其中8bpp和自定義模式由于顏色不足,需要接入顏色查詢表處理。自定義模式可以手動(dòng)對(duì)調(diào)色板的地址進(jìn)行預(yù)設(shè)來(lái)定義輸出的顏色。

時(shí)序模塊嚴(yán)格按照LCD的時(shí)序編寫(xiě),其中LCD時(shí)鐘為5 MHz。通過(guò)控制數(shù)據(jù)使能信號(hào)啟動(dòng)lcd_fifo數(shù)據(jù)輸出,逐行掃描顯示。同時(shí),設(shè)計(jì)該模塊時(shí),在數(shù)據(jù)有效信號(hào)(DE)有效前,須檢查lcd_fifo中是否存有數(shù)據(jù),以確定是否進(jìn)行數(shù)據(jù)讀取和傳輸;須進(jìn)行調(diào)色板模式設(shè)置,在幀傳輸過(guò)程中需要進(jìn)行模式鎖定,以免出現(xiàn)傳輸錯(cuò)誤;須根據(jù)不同bpp模式,確定不同的讀取時(shí)間段,18bpp每次都讀取,16bpp間隔1次讀取,8bpp間隔4次讀取。

3.5數(shù)據(jù)存儲(chǔ)模塊設(shè)計(jì)

本設(shè)計(jì)選用SD卡作為外接存儲(chǔ)硬盤(pán)。SD存儲(chǔ)卡具有大容量、高性能、安全性好等特點(diǎn)的多功能存儲(chǔ)卡,被廣泛用于數(shù)碼相機(jī)、掌上電腦和手機(jī)等便攜式設(shè)備中。SD卡上所有單元由內(nèi)部時(shí)鐘發(fā)生器提供時(shí)鐘,接口驅(qū)動(dòng)單元同步外部時(shí)鐘的DAT和CMD信號(hào)到內(nèi)部所用時(shí)鐘。SD卡有兩種通信協(xié)議,即SD通信協(xié)議和SPI通信協(xié)議,與SPI通信協(xié)議相比,SD通信協(xié)議的最大優(yōu)點(diǎn)是讀寫(xiě)速度快,單根數(shù)據(jù)線理論上可以達(dá)到25 MB/s,四線傳輸可以達(dá)到100 MB/s,本設(shè)計(jì)采用的是四線SD通信協(xié)議。

本設(shè)計(jì)中對(duì)SD卡的協(xié)議采用軟件編寫(xiě):首先在SoPC Builder里定義了6個(gè)I/O口:SD_CMD,SD_DAT0-DAT3,SD_CLK,分別對(duì)應(yīng)SD卡的命令、數(shù)據(jù)、時(shí)鐘端口,然后在NiosⅡIDE上按照SD卡的傳輸協(xié)議編寫(xiě)C程序來(lái)對(duì)6個(gè)I/O口進(jìn)行操作,以此來(lái)實(shí)現(xiàn)SD卡的傳輸協(xié)議。在完成SD卡數(shù)據(jù)塊的讀寫(xiě)基礎(chǔ)上移植了文件系統(tǒng)。FAT16,這樣在不影響讀寫(xiě)速度的條件下節(jié)省FPGA的資源。

3.6 數(shù)據(jù)傳輸模塊設(shè)計(jì)

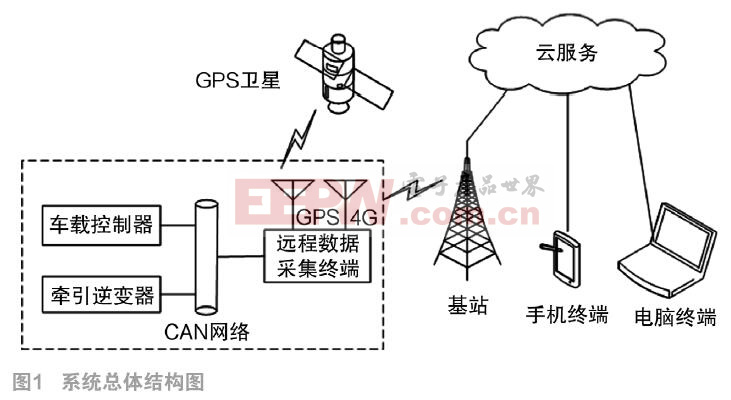

為了實(shí)現(xiàn)遠(yuǎn)程的數(shù)據(jù)交換,本系統(tǒng)采用以太網(wǎng)絡(luò)進(jìn)行數(shù)據(jù)傳輸。設(shè)計(jì)采用DM9000A作為以太網(wǎng)控制芯片。DM9000A是DAVICOM公司的一款高速網(wǎng)絡(luò)控制器,具有通用處理器接口、一個(gè)10/100M PHY和4kB的SRAM。為了實(shí)現(xiàn)數(shù)據(jù)的網(wǎng)絡(luò)傳輸,設(shè)計(jì)需要完成的任務(wù)有:在NiosⅡ上移植了μClinux操作系統(tǒng)、完成網(wǎng)絡(luò)底層驅(qū)動(dòng)程序的設(shè)計(jì)、基于網(wǎng)絡(luò)協(xié)議的應(yīng)用程序開(kāi)發(fā)。其中在NiosⅡ上移植了μClinux操作系統(tǒng)的工作已經(jīng)完成,因此本設(shè)計(jì)的關(guān)鍵任務(wù)是完成網(wǎng)絡(luò)驅(qū)動(dòng)程序設(shè)計(jì)與應(yīng)用程序開(kāi)發(fā)。

基于DM9000A的HAL設(shè)備驅(qū)動(dòng)設(shè)計(jì)主要分為兩步:首先是DM9000A的Avalon總線接口邏輯設(shè)計(jì);其次DM9000A的讀寫(xiě)驅(qū)動(dòng)程序設(shè)計(jì);最后按照HAL的驅(qū)動(dòng)模式將DM9000A的驅(qū)動(dòng)程序移植進(jìn)HAL。DM9000A是作為Avalon總線的從外設(shè)與NiosⅡ進(jìn)行通信。DM9000A的Avalon總線接口邏輯主要完成芯片信號(hào)與Avalon總線接口信號(hào)的對(duì)接。

DM9000A不允許直接訪問(wèn)芯片內(nèi)部的寄存器,需要通過(guò)數(shù)據(jù)端口和索引端口來(lái)讀寫(xiě)。而這兩個(gè)端口由CMD管腳控制:當(dāng)CMD接高電平時(shí)為數(shù)據(jù)端口,CMD接低電平為控制端口。

評(píng)論