低功耗8-bit 200MSPS時(shí)間交織流水線ADC

跟跟傳統(tǒng)二級(jí)放大器比有兩個(gè)優(yōu)點(diǎn)。第一,其增益要比傳統(tǒng)結(jié)構(gòu)的高。因?yàn)榈诙?jí)放大器是共源共柵放大器,所以輸出阻抗大,進(jìn)而增益也大。第二,因?yàn)榈诙?jí)是輸出級(jí),所以輸出級(jí)的極點(diǎn)是主極點(diǎn)。通過仔細(xì)的設(shè)計(jì),可以使主極點(diǎn)遠(yuǎn)離第一級(jí)的非主極點(diǎn)。這就意味著不需補(bǔ)償,減小了負(fù)載電容,所以與傳統(tǒng)放大器比,更小的電流可以獲得更高的帶寬。這對(duì)低功耗設(shè)計(jì)非常重要[6]。

本文引用地址:http://www.104case.com/article/197924.htm這里選用了開關(guān)電容共模負(fù)反饋,因?yàn)樗鄬?duì)連續(xù)時(shí)間共模負(fù)反饋更穩(wěn)定。這里有一個(gè)改動(dòng),即增加了SD1和SD2兩個(gè)開關(guān)。此設(shè)計(jì)減小了電荷注入和時(shí)鐘饋通的影響,所以電容C1和C2被的取值可以C3和C4一樣而不是遠(yuǎn)大于C3和C4。這種結(jié)構(gòu)可以實(shí)現(xiàn)更高的速度。

根據(jù)計(jì)算,增益和帶寬的要求可以通過公式計(jì)算得到,因?yàn)殡娐分幸粋€(gè)通道是8位100MSPS的,所以其增益要求為61dB,帶寬要求為794MHz。仿真結(jié)果如圖7所示。

其他電路

為了降低功耗,本設(shè)計(jì)采取了其它的一些功耗降低技術(shù)。首先,逐級(jí)遞減技術(shù)被應(yīng)用于本設(shè)計(jì)中。在流水線ADC中,前級(jí)的要求要比后級(jí)更嚴(yán)格,因?yàn)楹蠹?jí)產(chǎn)生的誤差會(huì)被前級(jí)的增益縮放。所以后級(jí)的電路并不需要前級(jí)電路那么嚴(yán)格的性能要求,例如放大器,開關(guān)和采樣電容。它們都可以以一個(gè)合適的因子進(jìn)行縮放。在本設(shè)計(jì)中,縮放因子為3/4,2/4,6/16,4/16;其次,對(duì)SH和MDAC電路中的開關(guān)數(shù)目進(jìn)行了優(yōu)化,相對(duì)于傳統(tǒng)結(jié)構(gòu),本設(shè)計(jì)用到的開關(guān)數(shù)目更少,減小了對(duì)時(shí)鐘驅(qū)動(dòng)能力的要求。

測(cè)試結(jié)果

該ADC采用0.35μm CMOS工藝,面積為4mm2,包括了所有輔助電路如基準(zhǔn)原的buffer,輸出buffer,pad,去耦MOS電容。兩條通道是左右對(duì)稱的。基準(zhǔn)產(chǎn)生電路在版圖的中間,時(shí)鐘產(chǎn)生電路在流水級(jí)的兩旁,這種布局是為了保證芯片的性能。

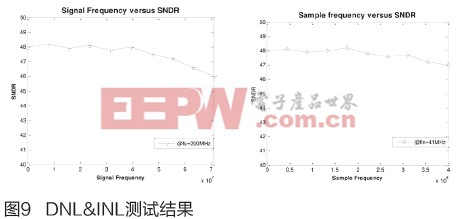

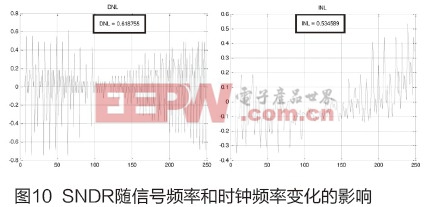

圖8是版圖。首先進(jìn)行了靜態(tài)測(cè)試。如圖9所示,DNL和INL分別小于0.61dB和0.53dB。其次,進(jìn)行了動(dòng)態(tài)測(cè)試,圖10是芯片的性能隨著輸入頻率和時(shí)鐘頻率變化的曲線。芯片的性能在輸入信號(hào)接近奈奎斯特頻率,時(shí)鐘頻率為300MHz時(shí)并沒有明顯下降。芯片的電流為40mA,不包括輸出buffer。

結(jié)論

本文設(shè)計(jì)了一個(gè)8-bit 200MSPS的流水線ADC。應(yīng)用了時(shí)間交織和逐級(jí)遞減技術(shù)。流水級(jí),放大器和基準(zhǔn)產(chǎn)生電路都經(jīng)過仔細(xì)的設(shè)計(jì)來保證在PVT變化時(shí)的性能。該流水線ADC工作在200MHz采樣頻率,41MHz信號(hào)頻率下時(shí),SNDR為47.7dB,在不包括output buffer的情況下電流消耗為40mA。

參考文獻(xiàn):

[1] Byung-Geun Lee, Byung-Moo Min A 14-b 100-MS/s Pipelined ADC With a Merged SHA and First MDAC IEEE journal of solid-state circuits, vol.43, No.12, December 2008

[2] H C Kim and D K J Kim, “A partially switched-opamp technique for high-speed low-power pipelined analog-to-digital converters” IEEE Trans Circuits Syst, I, Reg. Papers, vol. 53, no.4, pp. 795-801, Apr 2006

[3] D Y Chang and U K Moon, “A 1.4-V 10-bit 25MS/s pipelined ADC using opamp-reset switching technique” IEEE J. Solid-State Circuits, vol.38, no. 8, pp.1401-1404, Aug 2003

[4] John P Keane, Paul J Hurst, Stephen H, Lewis. “Background Interstage Gain Calibration Technique for pipelined ADCs”. IEEE Trans, Circuit Syst. I, Reg. Papers. Vol, 52, No 1. January 2005

[5] I Mehr and L Singer, “A 55-mw 10-bit 40-MSample/s Nyquist-rate CMOS ADC” IEEE J. Solid-state Circuits, vol.35m no.3, pp. 318-323, Mar 2000

[6] K Bult and G Geelen, ”A fast-settling CMOS opamp for SC circuit for 90-dB DC gain” IEEE J. Solid-state Circuits, vol.25, no.12, pp.1379-1384, Dec 1990

電子管相關(guān)文章:電子管原理

adc相關(guān)文章:adc是什么

模數(shù)轉(zhuǎn)換器相關(guān)文章:模數(shù)轉(zhuǎn)換器工作原理

負(fù)離子發(fā)生器相關(guān)文章:負(fù)離子發(fā)生器原理 電荷放大器相關(guān)文章:電荷放大器原理 離子色譜儀相關(guān)文章:離子色譜儀原理

評(píng)論