嵌入式車牌識(shí)別系統(tǒng)的設(shè)計(jì)及實(shí)現(xiàn)

1、引言

本文引用地址:http://www.104case.com/article/196662.htm隨著我國國民經(jīng)濟(jì)的高速發(fā)展,國內(nèi)高速公路、城市道路、停車場建設(shè)越來越多,對(duì)交通控制、安全管理的要求也日益提高,智能交通系統(tǒng)(Intelligent Transportation Systems,簡稱ITS)已成為當(dāng)前交通管理發(fā)展的主要方向,而車牌識(shí)別(License Plate Recognition,簡稱LPR)系統(tǒng)技術(shù)作為智能交通系統(tǒng)的核心,起著舉足輕重的作用,它在高速公路、城市道路和停車場等項(xiàng)目管理中占有無可取代的重要地位[1-2]。

本文所研究的車牌識(shí)別系統(tǒng),正是在這樣的背景下提出來的,對(duì)于目前LPR作為ITS中的核心關(guān)鍵技術(shù),具有相當(dāng)大的理論和現(xiàn)實(shí)意義。本系統(tǒng)所設(shè)計(jì)的是一個(gè)基于DSP和FPGA的嵌入式車牌識(shí)別系統(tǒng)[3-4],該系統(tǒng)不同于傳統(tǒng)的車牌識(shí)別系統(tǒng),具體實(shí)現(xiàn)過程將在下文詳細(xì)描述。

2、系統(tǒng)結(jié)構(gòu)設(shè)計(jì)

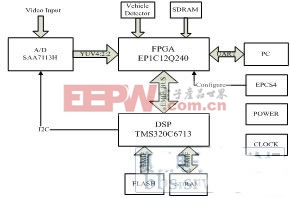

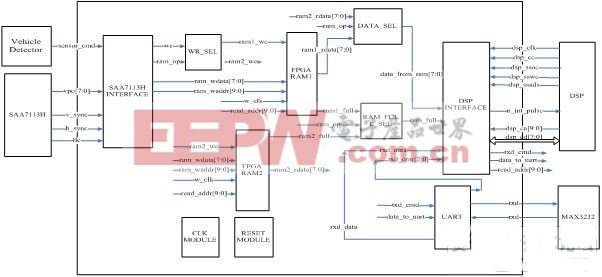

傳統(tǒng)的車牌識(shí)別系統(tǒng)主要采用攝像頭、視頻采集卡、工控機(jī)幾個(gè)主要模塊搭建出來的方法來實(shí)現(xiàn),其優(yōu)勢是實(shí)現(xiàn)容易,但是成本高、實(shí)時(shí)性不強(qiáng)、安裝和維護(hù)不便。而在本文系統(tǒng)設(shè)計(jì)中,摒棄了傳統(tǒng)的模式,采用TI公司的TMS320C6713B高性能(強(qiáng)大的并行運(yùn)算能力)DSP作為識(shí)別算法的運(yùn)行硬件平臺(tái),Altera公司性價(jià)比很高的Cyclone系列EP1C12Q240型號(hào)的FPGA作為協(xié)調(diào)整個(gè)系統(tǒng)的工作與相關(guān)的圖像采集及控制,再加上一些外圍器件(FLASH、SDRAM等)共同構(gòu)成本嵌入式車牌識(shí)別系統(tǒng)硬件平臺(tái),如圖1所示。

與傳統(tǒng)的車牌識(shí)別系統(tǒng)不同,該系統(tǒng)無需計(jì)算機(jī)即可實(shí)現(xiàn)車牌圖像的采集、識(shí)別、輸出結(jié)果,具有識(shí)別性能高、環(huán)境適應(yīng)性強(qiáng)、安裝維護(hù)簡單、成本低等特點(diǎn)。其中采用以DSP和FPGA作為核心的系統(tǒng)設(shè)計(jì)最大優(yōu)點(diǎn)是結(jié)構(gòu)靈活、通用性強(qiáng)、適合于模塊化設(shè)計(jì),從而能夠?qū)崿F(xiàn)高效率的算法和實(shí)時(shí)控制;同時(shí)其開發(fā)過程可以并行進(jìn)行。

圖1 車牌識(shí)別硬件框圖

2.1 視頻輸入模塊

目前,世界上實(shí)際應(yīng)用的電視信號(hào)制式主要有NTSC制、PAL制和SECAM制3種,世界上大多數(shù)國家采用PAL制,我國也采用PAL制,此系統(tǒng)采用的攝像頭輸出的視頻信號(hào)就是標(biāo)準(zhǔn)的PAL制式。

PAL電視制式規(guī)定,場掃描頻率為50Hz,每秒掃描25幀圖像,每幀包括奇、偶兩場圖像,每幀圖像的掃描行數(shù)為625行。電視信號(hào)由“圖像信號(hào)”和確保同步的“復(fù)合同步信號(hào)”以及消除掃描逆程回掃線的“復(fù)合消隱信號(hào)”等輔助信號(hào)構(gòu)成。PAL制電視信號(hào)轉(zhuǎn)化為數(shù)字視頻信號(hào)后,一般輸出數(shù)據(jù)格式符合ITU656 YUV4:2:2標(biāo)準(zhǔn),輸出一幀圖像的625行數(shù)據(jù)中,其中有效圖像數(shù)據(jù)占572行,其他為場消隱信號(hào);同樣,每行有效的圖像數(shù)據(jù)也只有720個(gè)象素。

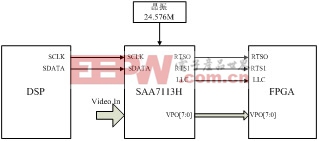

本系統(tǒng)中輸入是PAL制式的模擬圖像數(shù)據(jù),必須要經(jīng)過A/D轉(zhuǎn)換才能供后續(xù)系統(tǒng)處理。此系統(tǒng)選用的視頻解碼芯片(A/D)是Philips公司的SAA7113H[5],支持標(biāo)準(zhǔn)的PAL制式視頻信號(hào)輸入。輸入可以為4路CVBS或2路S視頻(Y/C)信號(hào),通過內(nèi)部寄存器的不同配置可以對(duì)輸入進(jìn)行轉(zhuǎn)換,輸出8位VPO總線及一些場、行同步控制信號(hào),其中輸出圖像數(shù)據(jù)為標(biāo)準(zhǔn)的ITU656 YUV4:2:2格式。SAA7113H內(nèi)部具有一系列寄存器,可以配置為不同的參數(shù),對(duì)色度、亮度等的控制都是通過對(duì)相應(yīng)寄存器改寫不同的值,寄存器的讀寫需要通過I2C總線進(jìn)行。由于TMS320C6713有自帶的I2C總線接口,所以系統(tǒng)設(shè)計(jì)里,利用DSP通過I2C總線對(duì)SAA7113H進(jìn)行配置控制,簡易了系統(tǒng)的設(shè)計(jì)[6]。

SAA7113H的VPO[7:0]總線以及RTS0、RTS1、LLCLK與FPGA相連,通過DSP的I2C總線把其中的RTS1、RTS0分別配置成場、行同步信號(hào),只有在行場同步信號(hào)都同時(shí)有效時(shí),才是有效的圖像數(shù)據(jù)輸出,否則一般為圖像的消隱信號(hào)。此時(shí)我們只要根據(jù)LLC時(shí)鐘來對(duì)VPO總線上的數(shù)據(jù)來采集即可得到完整的圖像數(shù)據(jù)(720*572大小)。SAA7113H與DSP和FPGA的連接方式如圖2所示。

圖2 SAA7113H與DSP和FPGA的連接示意圖

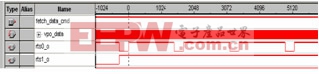

經(jīng)過實(shí)際操作,通過DSP的I2C總線對(duì)其進(jìn)行正確配置,然后由Verilog編寫的FPGA程序來進(jìn)行圖像數(shù)據(jù)的采樣,再用Quartus II自帶的SignalTap II Logic Analyzer(邏輯分析儀)對(duì)波形進(jìn)行相應(yīng)的分析,驗(yàn)證了系統(tǒng)中一些重要的信號(hào),結(jié)果顯示是正確可行的。圖3顯示的行、場同步信號(hào)RTS0、RTS1與VPO數(shù)據(jù)輸出的關(guān)系,達(dá)到了預(yù)期的結(jié)果。

圖3 行場同步信號(hào)(RTS0、RTS1)及VPO波形

2.2 DSP功能模塊

DSP作為本系統(tǒng)的核心芯片,主要有兩方面的關(guān)鍵技術(shù):一是DSP硬件平臺(tái)的搭建;二是DSP程序的開發(fā),包括DSP的算法移植及底層驅(qū)動(dòng)編寫。

2.2.1 DSP硬件搭建

TMS320C6713B是TI公司的一款高性能的32位浮點(diǎn)DSP[7]。其工作頻率最高可達(dá)300MHz,每秒可執(zhí)行2400MIPS和1800MFLOPS,非常適合在大數(shù)據(jù)量的圖像處理場合中使用。集成了豐富的片上外設(shè),包括PLL、多通道EDMA控制器、多通道緩沖串口(MCBSP)、I2C接口、HPI接口、EMIF接口等。其中32位高性能外部存儲(chǔ)器接口(EMIF)能與SRAM、SDRAM、SBSRAM等同步/異步存儲(chǔ)器進(jìn)行很方便的無縫連接接口,兼容8/16/32位外部存儲(chǔ)器總線[7]。本系統(tǒng)上的FLASH、SDRAM及FPGA都掛在DSP的EMIF總線上,方便DSP對(duì)其訪問和操作:

(1)DSP與FLASH接口:FLASH是一種高密度、非易失性的電可擦寫存儲(chǔ)器,主要用來存放一些應(yīng)用程序和其他信息,保證掉電不丟失數(shù)據(jù)。本系統(tǒng)采用的FLASH芯片為SST公司的SST39LF1601,其容量為2M字節(jié),可在3V~3.6V電壓下工作,存取速度為70ns。并把FLASH映射在DSP的CE1空間上,對(duì)應(yīng)的映射地址為0x90000000-0x901FFFFF。其中映射到CE1空間的好處是方便程序的BOOTLOADER,因?yàn)镈SP上電復(fù)位后,DSP內(nèi)部的EDMA控制器默認(rèn)會(huì)把CE1空間的1KB數(shù)據(jù)拷貝到地址0處的內(nèi)部存儲(chǔ)器中去,然后運(yùn)行。所以只要把應(yīng)用程序燒寫到FLASH中,系統(tǒng)就可以脫離計(jì)算機(jī)正常運(yùn)行。這里FLASH的另一個(gè)作用是保存用于車牌處理算法的一些字符模板信息、特征點(diǎn)信息以及一些用戶信息。

(2)DSP與SDRAM接口:SDRAM是同步動(dòng)態(tài)隨機(jī)存取存儲(chǔ)器(Synchronous Dynamic RAM)的縮寫,其主要特點(diǎn)為:一是同步訪問,讀寫操作都需要時(shí)鐘;二是動(dòng)態(tài)存儲(chǔ),芯片需要定時(shí)刷新。TMS320C6713的內(nèi)部存儲(chǔ)空間容量無法滿足系統(tǒng)程序的需要,而需要外擴(kuò)高速存儲(chǔ)器來提供系統(tǒng)程序的運(yùn)行空間。此系統(tǒng)中,使用了一片Hydix公司的16位SDRAM HY57V641620,其容量為8M,用于DSP對(duì)車牌進(jìn)行處理時(shí)的數(shù)據(jù)暫存,并把它映射到DSP的CE0空間上,對(duì)應(yīng)的地址為:0x80000000-0x807FFFFF。其工作時(shí)鐘由DSP提供,本系統(tǒng)設(shè)置為100MHz。通過配置DSP的EMIF控制寄存器,可以設(shè)置SDRAM的各種參數(shù)。

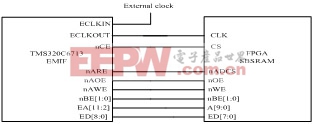

(3)DSP與FPGA的連接:FPGA從視頻流中捕獲了車牌圖像,如何讓DSP獲取該圖像信息進(jìn)行處理工作,也是本系統(tǒng)設(shè)計(jì)的一個(gè)重點(diǎn)。SBSRAM (Synchronous Burst Static RAM),即同步突發(fā)靜態(tài)存儲(chǔ)器,其最大的優(yōu)點(diǎn)就是支持同步突發(fā)訪問,訪問速度高,而且屬于靜態(tài)RAM,不需要刷新。所以,相對(duì)DSP來說,本系統(tǒng)把FPGA配置成SBSRAM來進(jìn)行訪問,會(huì)相對(duì)簡單些,并把其映射到DSP的外部CE3空間。由于本系統(tǒng)設(shè)計(jì)時(shí),對(duì)從FPGA讀取的圖像數(shù)據(jù)是以行單位來計(jì)算的,每次在FPGA內(nèi)部存滿一行數(shù)據(jù),F(xiàn)PGA就發(fā)一個(gè)中斷信號(hào)給DSP,讓DSP從中把數(shù)據(jù)通過EMIF口讀走,而這里一行的圖像數(shù)據(jù)的信息量為720*8bit,所以系統(tǒng)設(shè)計(jì)中,地址總線只用到了10位,而數(shù)據(jù)總線只用到了8位,對(duì)應(yīng)的映射到DSP的存儲(chǔ)地址為0xA0000000-0xA00003FF(1K Byte大小),這種設(shè)計(jì)方法很大程度上方便了DSP對(duì)FPGA的訪問操作,F(xiàn)PGA與DSP的連接如圖4所示。

圖4 FPGA與DSP硬件連接示意圖

2.2.2 DSP軟件編寫

DSP作為信號(hào)處理芯片,在處理各種信號(hào)方面都有著強(qiáng)大的優(yōu)勢。本系統(tǒng)中,大部分圖像處理算法(車牌定位、分割、字符識(shí)別等)都在其上實(shí)現(xiàn)。在搭建好良好的硬件平臺(tái)后,接下來要做的就是對(duì)DSP的編寫,這里主要有兩塊程序的編寫:算法的移植和底層驅(qū)動(dòng)的開發(fā)。

CCS(Code Composer Studio)是TI公司推出的一套集成開發(fā)環(huán)境,用它來開發(fā)TI的DSP芯片應(yīng)用程序;其中CCS 中集成的DSP/BIOS[8]是TI公司為C5000系列和C6000系列數(shù)字信號(hào)處理芯片量身定制的一個(gè)嵌入式實(shí)時(shí)操作系統(tǒng)內(nèi)核,具有圖形化界面、代碼快速成型功能以及完備的API函數(shù)庫等優(yōu)勢,可極大的方便應(yīng)用系統(tǒng)的開發(fā)和在線調(diào)試。本系統(tǒng)就是采用CCS2.2中自帶的DSP/BIOS操作系統(tǒng)進(jìn)行程序的開發(fā),使用任務(wù)、線程、旗語、郵箱等進(jìn)行一系列編程,方便的控制程序的實(shí)時(shí)調(diào)度運(yùn)行。

(1)算法移植:一般算法的編寫都會(huì)在Matlab上實(shí)現(xiàn),雖然它是一種類C語言,但和標(biāo)準(zhǔn)的C相比還是有著很多的差異,而且Matlab中往往提供了各種信號(hào)處理的工具箱,如圖像處理、神經(jīng)網(wǎng)絡(luò)、小波變換等等。我們只要簡單的調(diào)用這些函數(shù)來,帶入幾個(gè)參數(shù)即可以方便的進(jìn)行各種信號(hào)處理。所以,當(dāng)把這些算法移植到本系統(tǒng)的DSP中時(shí),一些函數(shù)還得重新編寫,還有編程格式、風(fēng)格都要有所更改,有些地方為了提高算法的效率,充分利用DSP的資源,還應(yīng)該把部分代碼編寫成匯編語言等等。當(dāng)把整個(gè)算法都移植完后,最后封裝成一個(gè)函數(shù),這樣更易于整個(gè)算法的維護(hù)及調(diào)用。然后,當(dāng)觸發(fā)條件滿足時(shí),用DSP/BIOS中的某個(gè)任務(wù)來調(diào)用這個(gè)算法處理函數(shù)來完成對(duì)車牌圖像的識(shí)別。

(2)底層驅(qū)動(dòng)的開發(fā):底層驅(qū)動(dòng)的編寫采用CCS自帶的CSL(Chip Support Library)來進(jìn)行底層驅(qū)動(dòng)開發(fā),CSL提供一系列應(yīng)用程序接口(API,Application Programming Interface)用于配置和控制DSP片上外設(shè),從而簡化了DSP片上外設(shè)的開發(fā)工作,大大縮短了開發(fā)周期。

2.3 FPGA功能模塊

FPGA是英文Field Programmable Gate Array的縮寫,即現(xiàn)場可編程門陣列,它是在PAL、GAL、EPLD等可編程器件的基礎(chǔ)上進(jìn)一步發(fā)展的產(chǎn)物。FPGA的使用非常靈活,同一片F(xiàn)PGA通過不同的編程數(shù)據(jù)可以產(chǎn)生不同的電路功能。FPGA在通信、數(shù)據(jù)處理、網(wǎng)絡(luò)、軍事和航空航天等眾多領(lǐng)域得到了廣泛應(yīng)用。

本系統(tǒng)設(shè)計(jì)中,F(xiàn)PGA作為圖像采集、存儲(chǔ)以及傳輸?shù)暮诵哪K,協(xié)調(diào)及控制著整個(gè)系統(tǒng)的正常運(yùn)行,起著非常重要的作用。本系統(tǒng)選用了Altera公司性價(jià)比較高的Cyclone系列中的EP1C12Q240型號(hào)FPGA。該FPGA共有52個(gè)存儲(chǔ)塊,共239616bits。通過QUARTUS II自帶的MegaWizard工具可以將每個(gè)塊配置成不同的存儲(chǔ)模式,如單口RAM、簡單雙口RAM、移位寄存器、ROM和FIFO等,這樣有利于本系統(tǒng)在采集圖像時(shí)暫存圖像數(shù)據(jù)及把FPGA作為SBSRAM供DSP訪問的設(shè)計(jì)。該FPGA有著片上足夠多的IO口也為本系統(tǒng)以后擴(kuò)展留下了空間。

這里與FPGA相連的器件有:SAA7113H、SDRAM、DSP以及MAX3232。由于FPGA純粹是一個(gè)編程器件,其IO腳可以配置成任何我們需要的信號(hào),與任何接口可以相接,所以硬件接口設(shè)計(jì)上比較簡單。難點(diǎn)在于編寫各種通信協(xié)議和不同的接口進(jìn)行無縫傳輸。整個(gè)FPGA的程序設(shè)計(jì)總體框圖5所示:方框內(nèi)的部分為FPGA的各個(gè)模塊以及它們之間的相互連接。方框以外的部分是FPGA的外圍器件。

圖5 FPGA的程序設(shè)計(jì)總體框圖

該FPGA系統(tǒng)在整個(gè)車牌識(shí)別系統(tǒng)中起到圖像的采集、緩存和傳輸?shù)墓δ堋.?dāng)車輛檢測器的感應(yīng)信號(hào)sensor_cmd信號(hào)有效時(shí),啟動(dòng)SAA7113H_INTERFACE模塊內(nèi)部的狀態(tài)機(jī)進(jìn)行圖像的采集工作,SAA7113H_INTERFACE模塊從SAA7113H的視頻流中檢測到場開始信號(hào)時(shí),開始一幀圖像數(shù)據(jù)的傳輸。由于視頻流為PAL制,所以一幀圖像分為奇場和偶場兩場圖像數(shù)據(jù)。

系統(tǒng)采用了乒乓結(jié)構(gòu)的設(shè)計(jì)方法,這種典型的設(shè)計(jì)方法在“以面積換速率”的FPGA設(shè)計(jì)方法中經(jīng)常得到應(yīng)用。由于EP1C12Q240C8內(nèi)部共有52個(gè)存儲(chǔ)塊,共239616bits,所以在FPGA內(nèi)部設(shè)計(jì)一個(gè)小存儲(chǔ)量的RAM是可行的。系統(tǒng)中設(shè)計(jì)了兩塊720*8bits(每行圖像數(shù)據(jù)大小)的空間,這兩個(gè)存儲(chǔ)器的寫時(shí)鐘信號(hào)是SAA7113H輸出時(shí)鐘LLC的2倍。SAA7113H INTERFACE模塊通過與SAA7113相連的VPO總線,采集標(biāo)準(zhǔn)的YUV4:2:2的Y分量(只采集Y分量目的是得到灰度圖像),即其中的亮度信號(hào),一行的圖像含有720個(gè)亮度信息,亮度信息的位寬為8位。當(dāng)FPGA_RAM1的圖像行滿時(shí),發(fā)出行滿信號(hào)ram1_full給DSP_INTERFACE模塊,在DSP_INTERFACE模塊中將該信號(hào)轉(zhuǎn)好為中斷信號(hào)n_int_pulse以通知DSP調(diào)用EDMA獲取該行的圖像。同時(shí)進(jìn)行內(nèi)部RAM的切換,把下一行數(shù)據(jù)寫入FPGA_RAM2中,保證一邊DSP在讀取一行圖像數(shù)據(jù),一邊FPGA在寫入下一行圖像數(shù)據(jù)給另一個(gè)RAM ,以完成一次乒乓操作。

DSP在完成車牌圖像的處理后,將車牌圖像的識(shí)別結(jié)果通過EMIF寫回到FPGA的DSP_INTERFACE模塊內(nèi)部的寄存器里,并通過UART模塊獲取這些寄存器的值,通過UART傳到PC。

圖6所示波形是圖5內(nèi)部框圖中的其中一個(gè)SAA7113_INTERFACE模塊在Modelsim上的仿真波形,從仿真波形中看出,與實(shí)際SAA7113輸出波形是符合的,達(dá)到我們預(yù)期的結(jié)果。

圖6 SAA7113_INTERFACE仿真波形

3、結(jié)論

本文所設(shè)計(jì)的基于DSP和FPGA的嵌入式車牌識(shí)別系統(tǒng),具有速度快、穩(wěn)定性高、體積小、功耗低等特點(diǎn),為車牌識(shí)別算法提供一個(gè)較好的驗(yàn)證平臺(tái),如圖7所示。經(jīng)過驗(yàn)證,該車牌識(shí)別系統(tǒng)能夠?qū)崿F(xiàn)實(shí)時(shí)的圖像采集、傳輸、識(shí)別。從時(shí)間上來考慮,在DSP內(nèi)部單對(duì)一幅車牌圖像完成處理(定位、歸一化、特征提取與編碼)只需不足400ms的時(shí)間,速度上來說是非常快的;從識(shí)別率上來考慮,只要算法達(dá)到一定的要求,經(jīng)過該車牌識(shí)別系統(tǒng)運(yùn)算后,識(shí)別率也是能達(dá)到非常高的。總之,該系統(tǒng)在車牌識(shí)別方面有著一定的應(yīng)用價(jià)值。

最后,作為一個(gè)可以實(shí)際使用的車牌識(shí)別系統(tǒng),在以后的系統(tǒng)設(shè)計(jì)中,還需要增加用于網(wǎng)絡(luò)通訊的部分、及一些更智能化的功能,如液晶顯示、聲音提示等等。總之,嵌入式車牌識(shí)別系統(tǒng)是當(dāng)前智能交通應(yīng)用領(lǐng)域的重要研究課題之一,擁有廣闊的應(yīng)用前景。

![]()

圖7 車牌識(shí)別系統(tǒng)實(shí)物圖

參考文獻(xiàn)

[1] 陳友仁.圖像中車牌自動(dòng)識(shí)別的研究[D].上海: 上海交通大學(xué),2001: 1-10.

[2] 劉玲, 張興會(huì). 智能化車牌識(shí)別系統(tǒng)研究[J]. 儀器儀表學(xué)報(bào), 2004, 25(4)增刊:565-567.

[3] 蘇厚勝. 車牌識(shí)別系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn)[J]. 機(jī)器視覺, 2006, (3): 103-107.

[4] 洪健, 陳繼榮. 基于DSP+CPLD的車牌實(shí)時(shí)識(shí)別系統(tǒng)的設(shè)計(jì)[J]. 計(jì)算機(jī)應(yīng)用研究, 2007, 24(7): 218-219.

[5] 孔祥剛, 諸靜, 陽濤.SAA7113H在視頻采集接口設(shè)計(jì)中的應(yīng)用[J]. 電子技術(shù), 2003, (12): 26-29.

[6] 張占鵬, 蘇秀琴, 呂帥華. 基于TMS320C620X系列DSP的SAA7113H控制實(shí)現(xiàn)[J]. 科學(xué)技術(shù)與工程, 2006, 6(12): 1693-1695.

[7] 李方慧, 王飛, 何佩琨.TMS320C6000系列DSPs原理與應(yīng)用[M]. 北京:電子工業(yè)出版, 2005: 337-380.

[8] 宋勝利, 曾巒. DSP/BIOS在數(shù)字圖像處理中的應(yīng)用[J]. 國外電子測量技術(shù), 2005,24(12):33-36.

linux操作系統(tǒng)文章專題:linux操作系統(tǒng)詳解(linux不再難懂)存儲(chǔ)器相關(guān)文章:存儲(chǔ)器原理

評(píng)論