數字測試儀下的參數測試單元的設計

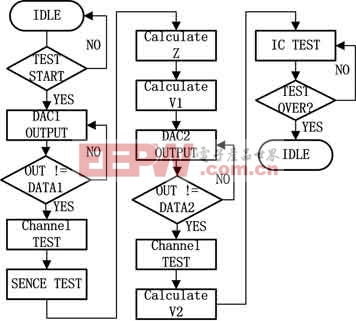

之前提到過為了提高參數測量的精度,采用了兩套精度校對方案分別從代碼校對和硬件控制兩個方面對測量過程進行監控和校對。代碼校對是根據實際的測試經驗來提高測試精度。硬件控制則具體分為兩個器件手冊說明,在測試流程中加入校準參數步驟進行,第一個步驟是輸出過程中加入以比對為基礎的PID算法,將ADC回采的實際輸出電壓值和根據輸入數據得到的理論輸出值進行比較,然后進行相應的補償,以保證輸出準確。第二個步驟是采用Kelvin四線橋接技術,首先控制參數測量單元評估從測試儀輸出端到DUT的傳輸線阻抗,再在后級測試中進行屏蔽,從而提高整個系統的測試精度。具體的測試控制流程如圖5所示。本文引用地址:http://www.104case.com/article/195864.htm

圖5 參數測試流程

2 測試流程

流程說明:測量單元進入測量模式,同時檢測是否得到FIPMU或者FVPMU命令,當檢測到命令時,輸出對應信號,同時根據PMUSETFILTER命令中的檢測次數,校驗輸出信號。經過規定次數下的校驗無誤后,開啟相關測試通道進行后級測試。后級測試根據Kelvin原理,對測試通道的傳輸阻抗先進行預估。根據得到的預估值Z,校對測試電壓并最終得到在該測試通道下的準確模擬參數V1。然后根據同樣的原理,對其他要求的通道進行預估,得到相應的阻抗預估值Zn,從而最終得到各個測量通道的準確測量參數。需要說明的一點是由于測試是一個連續的過程,因而每個測量通道阻抗的預估在一整套多芯片的測量中只需要一次。而不必對每個芯片引腳的測試通道反復預估,這樣可以節約測試時間和成本。

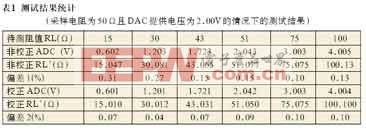

試驗分析

為了驗證參數測量單元在負載為小電阻情況下的工作情況,筆者在常溫環境下針對不同阻抗的待測單元,分別用無校準IC參數測試單元和校準后的參數測試單元進行測試比對,測試結果如表1所示:校準后的測量單元借助Kelvin技術在小電阻測量的優勢,能夠在低于50Ω的負載測量中,保持至少提升一個數量級的測量精度優勢。而當電阻提高越多,精度優勢就越不明顯。

根據Kelvin技術的理論可以知道其優勢主要在于可以有效評估傳輸線阻抗帶來的測量誤差。而當傳輸線阻抗一定,負載增大時,傳輸線阻抗造成的壓降占總測試電壓的比例下降,測試精度的提升程度也會隨之下降。

結束語

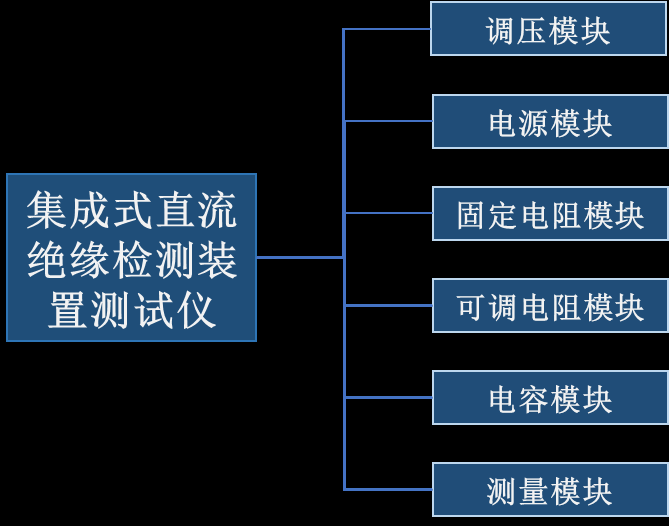

針對數字測試中面臨的參數測試要求,本文提出了基于FPGA控制,32位PCI通信同時具備高精度輸出和采樣芯片的參數測量單元,并對實現過程中的具體問題進行了分析。

評論