基于LabVIEW與USB的虛擬儀器接口設計

0 引 言

LabVIEW是一種基于圖形程序的虛擬儀器編程語言,與傳統儀器相比,虛擬儀器技術以計算機為平臺,在程序界面中有用于模擬真實儀器面板的控件可供調用,可用于設置輸入數值、觀察輸出值以及實現圖表、文本等顯示,因此具有友好的人機界面。LabVIEW具有強大的數據采集、分析、處理、顯示和存儲功能。在測試與測量、數據采集、儀器控制、數字信號分析、工廠自動化等領域獲得了廣泛的應用,顯示出其強勁的生命力。LabVIEW平臺下開發的虛擬儀器在相同硬件條件下,改變軟件即可實現不同的儀器功能,真正實現了“軟件即儀器”的設計理念。

實現LabVIEW對數據的采集和處理,傳統的方法是采用數據采集卡,但是這些數據采集卡設備存在安裝不便,價格昂貴,受計算機插槽數量、地址、中斷資源的限制,可擴展性差等缺點。在LabVIEW平臺下使用USB總線進行數據傳輸,由于USB接口總線具有即插即用,接口簡單,傳送速率高等特點,因此基于Lab-VIEW和USB接口的虛擬儀器具有靈活、可靠、經濟等特點。

鑒于以上LabVIEW和USB接口儀器的優點,實現LabVIEW下USB接口的接口程序就顯得尤為重要。在此,介紹了一種基于LabVIEW與USB的虛擬儀器接口設計的方法。

1 設計方案

由于各類基于USB總線的數據采集、控制的虛擬儀器都涉及到LabVIEW與USB接口程序的設計,為了不失一般性,這里以虛擬示波器為例,介紹該接口程序的設計方法。

1.1 硬件設計方案

該系統是虛擬示波器,主要工作是采集被測模擬信號,并將信號通過USB2.o接口傳輸到PC104計算機,運行計算機LabVIEW平臺下的應用軟件完成數據的處理與記錄,并在顯示器上繪制曲線。

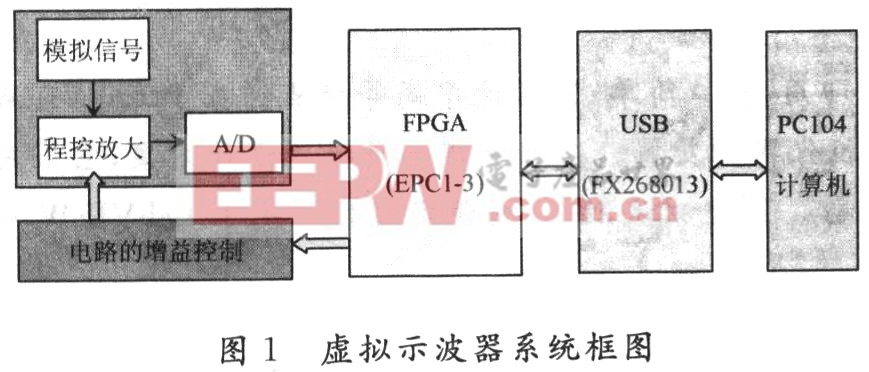

該系統主要由模擬信號采集模塊、FPGA控制模塊、USB傳輸模塊和計算機組成,其系統結構框圖如圖1所示。

1.1.1 FPGA控制模塊

該設計采用Alter公司的Cyclone系列現場可編程門陣列(Field Programmable Gate Array,FPGA),芯片EP1c3T144來實現高速數據控制及傳輸。

EP1C3T144采用TPFQ封裝,擁有100個I/O口和2 910個邏輯單元,是一種高密度、高性能的FPGA。

FPGA的主要功能是高速數據采集、數據幀控制,以及與USB單片機進行通信。具體說明如下:

(1)高速數據采集及增益控制。高速數據采集功能是控制高速A/D的時序進行數據采集;增益控制功能是通過向程控增益放大電路發送控制命令,進而達到控制模擬電路放大倍數的目的。由于篇幅關系,有關這兩個方面的內容不做詳細介紹。

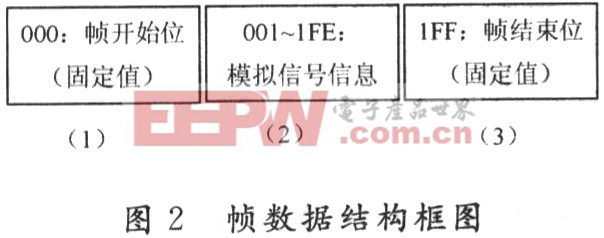

(2)數據幀控制。FPGA每秒向PC機發送100幀和每幀512 B的數據,將如此高速的數據進行準確無誤的控制和傳輸是系統的技術難點之一。該方案中,每幀數據由3部分組成:如圖2所示。

其中,每一幀數據的開始位和結束位是固定數據,計算機的測井應用軟件判斷接收到每一幀數據的幀頭及幀尾是否錯誤。若出現錯誤,將該幀數據丟棄,同時準備接收下一幀數據。數據第二部分,模擬信號由FPGA控制A/D芯片采集得到。

1.1.2 USB傳輸模塊

Cypress公司的。EZ-USB FX2芯片CY7C68013是一款性能較高的USB 2.0微控制器。在單片機上集成USB 2.O收發器、SIE(串行接口引擎)、增強的8051微控制器和可編程的外圍接口。EZ-USB FX2中的智能SIE可以處理大部分USB 2.0協議,使得微控制器可以專注于應用功能,從而減少了開發時間,確保了USB的兼容性。

CY7C68013有3種可用的接口模式:端口、GPIF主控和Slave FIFO方式。在該系統中,根據系統對數據傳輸速度和實時性的要求,配置CY7C68013工作的接口模式為Slave FIFO模式。在Slave FIFO模式下,外部邏輯或外部處理器直接與FX2端點FIFO相連。這種模式下,外部主控器FPGA通過異步方式與CY7C68013進行數據通信。

FPGA與CY7C68013之間的硬件接口框圖如圖3所示。SL_WR/SL_RD是Slave FIFO的寫使能/讀允許信號。FPGA向CY7C68013提供Slave FIFO輸出允許信號SL_OE,僅在數據輸出時有效。FB[7:O]為8位雙向數據總線。ADDR[1:0]為FIFO端點選擇信號。在數據輸入時固定為00,選擇的是端點2;在數據輸出時固定為10,選擇的是端點6。

評論