一種2 Gsps數字示波器數據采集系統的設計

數據采集系統是數字存儲示波器的核心部分,在示波器采集控制電路的控制下,數據采集系統將待測的模擬信號量化后進行緩存,供示波器軟件系統進行數據的處理、運算、顯示。隨著計算機技術的不斷發展,高速ADC的性能不斷提高,功能強大的DSP信號處理的實時性越來越強,可編程的邏輯器件的性能不斷提升,為示波器數據采集系統的實現提供了一個可靠而且實用的數字平臺。相應的,數據采集系統的采樣速率、存儲深度、波形捕獲能力、鑒別能力等指標也在不斷提高。國際上,示波器行業像安捷倫、泰克等公司在數字存儲示波器市場上占據了主導地位,均有實時采樣率達到幾十Gsps的示波器面市,但是由于受到器件和工藝的限制,國內實現真正的高速高分辨率的數據采集系統還具有比較大的困難。

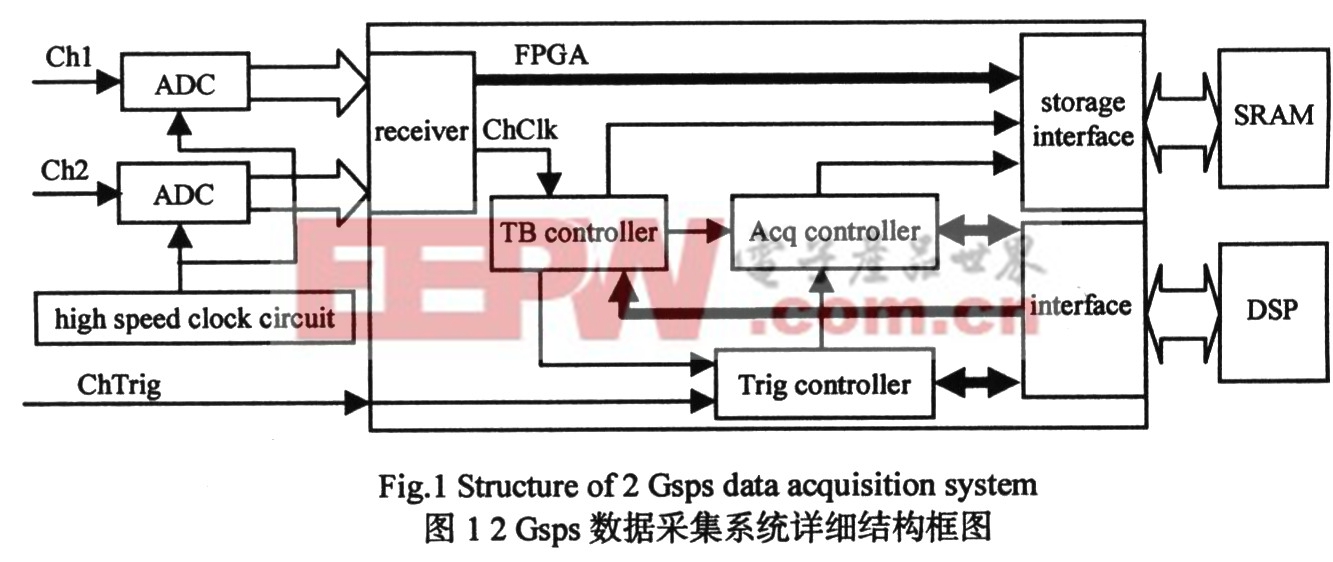

本文采用ADC+高頻時鐘電路+FPGA+DSP的結構模式,設計了一種實時采樣率為2 Gsps的數字存儲示波器數據采集系統,為國內高速高分辨率的數據采集系統的研制提供了一個參考方案。

1 關鍵器件選擇

DSO數據采集系統的主要技術指標:a)雙輸入通道同時工作,每通道最高實時采樣率達到2 Gsps;b)垂直分辨率8 bit;c)存儲深度:8 MB/CH。整個系統的關鍵器件包括ADC、高頻時鐘芯片、FPGA、DSP、SRAM。通過對目標系統主要技術指標的分析,結合數字存儲示波器的應用特性,選擇了以下一系列器件。

數據采集系統要求達到的最高實時采樣率為2 Gsps,同時考慮目標系統所要求的垂直分辨率、數據輸出格式,另外兼顧示波器的模擬帶寬以及器件的購買渠道和性價比,選擇了Atmel公司的AT84AD001。AT84AD001是雙通道ADC,每一通道具有1 Gsps的實時采樣率,在交錯模式下雙路ADC并行采樣可以達到2 Gsps的實時采樣率。其分辨率為8 bit,數據輸出格式是LVDS(Low Voltage Differential Signaling),具有1:1數據輸出或1:2數據輸出模式可選,此外,全功率輸人帶寬(-3 dB)為1.5 GHz,差分電壓輸入范圍為500 mVVpp。

此外,重要的一點,AT84AD001還具有FISDA(Fine Sampling Delay Adjustment on Channel Q)功能,通過調整Q通道的采樣時刻,有效地避免了因為采樣時鐘的占空比不等于50%而造成的誤差,保證了采樣精度。

高速高精度的ADC對采樣時鐘的精度要求非常高,時鐘電路一般的設計方法是直接利用FPGA內部的鎖相環倍頻電路產生,但是目標系統要求采樣時鐘頻率達到1 GHz,而目前Altera和Xilinx公司的高端FPGA其I/O輸出頻率最高只能達到800MHz。經過綜合評價,最終選定了美國NS公司的高頻時鐘芯片LMX2531LQ1910E。其輸出低段頻率為917 MHz~1 014 MHz,滿足設計要求,此外,LMX2531具有非常低的抖動和相位噪聲。而且還集成了低噪聲、高性能的低壓差線性穩壓器LDO(Low Drop Out regulator)元件,使電路的抗干擾性和穩定性得到了提高。

FPGA的可編程性以及豐富的內部邏輯資源和外部I/O資源,用來作為數字存儲示波器數據采集與控制系統。特別地,單片AT84AD001量化輸出是16路1 Gbps速率、LVDS格式的差分數據,目標系統雙輸入通道同時工作,這就要求FPGA具有32個能支持1 Gbps的差分I/O,利用高速I/O將數據接收并存儲。由此,選擇了Altera公司的Stratix II EP2S60F1020C4,該FPGA最多可以支持多達84個1 Gbps的差分通道,并且增加了源同步通道的動態相位對準電路,為高速數據的接受提供了有力的支持。

在示波器的高速數據采集系統中,需要對采集到的數據進行大量實時性的運算和處理,綜合考慮市面上的各

款處理器,選擇ADI公司的DSP芯片Blackfin561作為嵌入式計算系統。Blackfin561主頻最高可達750 MHz,其內核包含2個16位乘加器MAC(Multiplier and Accumulator)、2個40位累加器ALU、1個40位移位器、100KB的片內L1存儲器以及128 KB的片內L2存儲器SRAM,同時具有動態電源管理功能。此外,Blackfin處理器還包括豐富的外設接口,滿足設計的需要。

本文設計的數字存儲示波器的存儲深度要求達到每通道8 MB,而FPGA芯片Stratix II EP2S60F1020C4的片內存儲單元總共只有552 KB,所以,必須采用片外存儲器作為采集RAM來存儲量化后的波形數據,經過綜合考慮,選用美國賽普拉斯公司的SRAM芯片CY7C1440AV33。

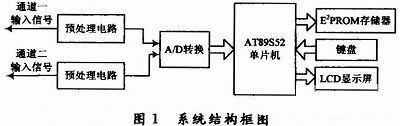

2 系統結構

本文設計的數據采集系統采用ADC+高速時鐘電路+FPGA+SRAM+DSP的結構模式,其系統結構如圖1所示。通道1、通道2均采用一片最高實時采樣率為2 Gsps的AT84AD001作為模數轉換器完成對模擬輸入信號的量化,高頻時鐘電路用來產生整個數據采集系統所需要的工作時鐘,FPGA用來完成采樣數據的接收,并且實現FPGA與DSP的接口電路;SRAM作為數據采集系統的采集RAM,完成將量化后的波形數據緩存;DSP作為數據采集系統的主控機,完成對采集電路的控制和接收采集電路采集的數據,并對采樣數據進行處理、分析和顯示。

評論