基于PCI Express接口的數據 采集存儲系統設計

TTL引腳S_DATA為配置串行移位寄存器的輸入端,串行寄存器可在每一個S_CLOCK信號的上升沿對S_DATA信號進行取值。另有一配置鎖存器可在S_LOAD信號為高電平時鎖存串行移位寄存器的內容。這樣,通過設置S_DATA信號的值(即T2…T0,N1,N0,M8…M0的數值)以及三信號線的時序,便可控制SY89429AZC時鐘芯片輸出精確的采樣時鐘。

2.2 FPGA邏輯控制

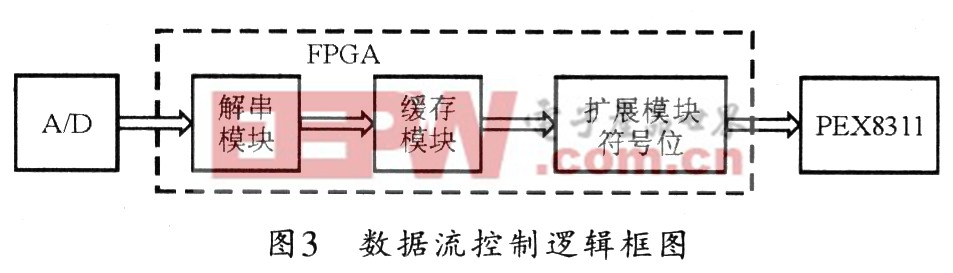

邏輯控制模塊要實現的主要功能是解析上位機控制信息并發送控制命令,同時要程控采樣時鐘頻率,還要對采集數據流進行處理和傳輸。其中數據流邏輯控制模塊中的功能組成直接關系到高速采集信號能否實時可靠的傳輸。圖3所示為數據流的邏輯控制結構框圖。

本設計選用Cyclone II系列芯片EP2C5Q208。此芯片為208腳PQFP封裝,用戶可用I/O資源高達158個,差分通道數為58個,其內部邏輯資源、M4K存儲資源、內部PLL數量完全能夠滿足本系統設計的需要。

由于AD轉換芯片AD94301的采樣精度為12位,而PEX8311接口芯片可支持8位、16位、32位數據位。因此,為了更加有效的提高數據傳輸的效率,同時也為了使數據采集速率獲得相對提升,設計中的PEX8311采用32位數據位模式進行數據傳輸。這樣,在本方案的FPGA數據流邏輯控制中,不僅要進行數據的緩存以及數據傳輸邏輯的控制,還要進行數據位的變換擴展,即由12位數據擴展為32位數據。為了實現數據位由12位到32位的轉換,應先把解串后的12位采樣數據進行數據分流模塊,以把12位數據交替存儲到兩個FIFO中緩存。圖4所示是經數據分流模塊交替產生12位數據的仿真示意圖。

高速數據采集系統中的數據傳輸速率與A/D轉換器的采集速度很難保持一致。為了協調數據采集與數據傳輸之間的速度差異,一般都在兩者之間加入數據緩存器進行緩沖,使前端的數據采集與數據傳輸可以異步工作。通常的做法是在A/D轉換后將數據送至外置的FIFO或雙口RAM中進行緩存。但這樣無疑會增加布線密度,同時降低數據傳輸的可靠性。EP2C5Q208 Cyclone II系列FPGA提供了多達26塊的M4K RAM,而且PCI Ex-press總線的傳輸速率也大于數據采集速率,所以,可在FPGA內部設置FIFO空間來實現對數據的緩存。這樣,從FIFO讀出的兩組12位數據經過符號位擴展模塊后,即可擴展變換為32位數據并由FPGA并行輸出到PCI Express接口模塊。

2.3 PCI Express接口控制

由于數據采集速率隨著芯片技術的進步而不斷提高,而大量的數據必須傳輸至主機進行處理。這些傳輸都由那些將設備連接到主機內存的數據總線完成。因此,數據總線傳輸的速率常常成為整個數據采集系統的瓶頸,這也是許多儀器帶有昂貴板載內存的主要原因之一。而PCI Ex-press的出現,可使測量設備至主機內存的數據傳輸速率達到一個前所未有的高度。

PCI Express又稱3GIO,即第三代輸入/輸出接口的意思。串行數據傳輸可使數據傳輸速率達到驚人的2.5 Gbps (PCI Express 1.0規范),且采用全雙工數據傳輸,并可擴展為×1、×4、×8、×16通道模式。

以PCI Express×1來計算,扣除數據校驗冗余8 bit\10 bit,有效數據傳輸率可以達到200 Mbyte,理論上可以提供100 MHz采樣速率和雙字節以內的采樣精度的傳輸帶寬。

目前,實現PCI Express總線接口控制的方法有兩種:一種是采用FPGA/CPLD來實現。目前,Altera等專業FPGA公司都提供了多種PCI Express總線接口實現方案,并提供了相應的MegaCore。但是這種方案設計難度大,調試困難;另一種是采用專用接口芯片,如利用PLX公司的PEX8311來實現局部總線與PCI Express總線的連接。目前,無論從技術還是成本來看,第二種方案都是比較理想的選擇。

PEX8311芯片符合PCI Express 1.0基本規范,它支持主模式、從模式以及DMA三種數據傳輸方式。PEX8311芯片的主要特性如下:

◇集成有單通道、全雙工2.5 Gbit/s傳輸的PCI Express端口;

◇可配置局部總線寬度,支持8位、16位和32位的總線方式;

◇支持數據總線、地址總線獨立和復用總線操作模式;

◇雙通道高性能的DMA數據傳輸可支持數據塊模式、分散/集中模式、硬連線數據傳輸模式和命令模式;

◇支持PCI Express規范中的端點和根復合體模式;

◇芯片小型封裝,適合緊湊的電路板設計。

本方案中主要使用DMA方式中的命令模式。在命令模式下,可以通過一對硬連線“DREQ”和“DACK”來控制傳輸,每一個DMA通道都有一對這樣的信號。當FIFO在被寫滿或讀空時,命令模式將暫停操作。而當FIFO狀態改變以后,又可繼續行進數據傳輸。

評論