一種高精度中頻信號數據采集卡的硬件設計

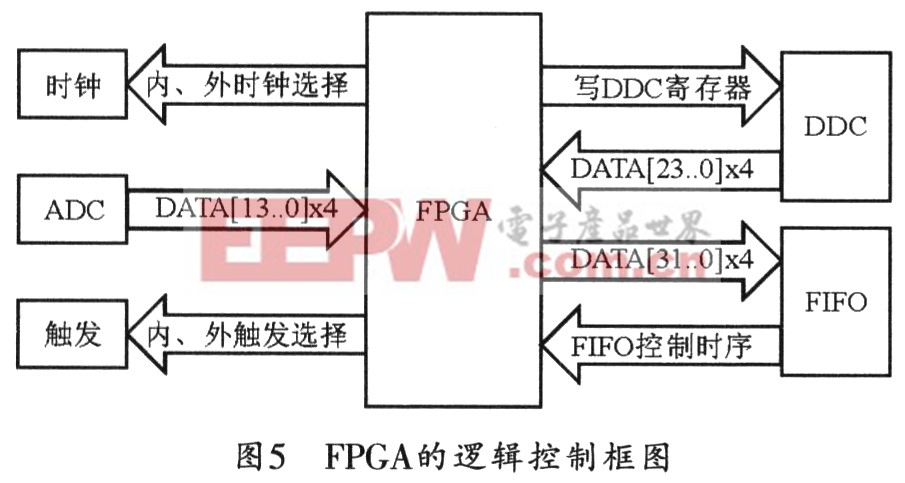

FPGA是本采集卡的核心模塊,可由時鐘及觸發源控制、DDC控制、數據處理、FIFO存儲控制等模塊組成,圖5所示是其邏輯控制框圖。本文引用地址:http://www.104case.com/article/195595.htm

時鐘及觸發控制模塊主要用于完成內、外時鐘源選擇,內、外觸發源選擇以及數據通路選擇等控制命令的接收和發送;

DDC控制模塊是采集卡最重要、也是最具獨創性的部分,它主要完成對GC4016芯片255個32位寄存器的控制字發送,從而實現其內部模塊功能,其核心控制指令是載波頻率、相位信息、增益控制、各濾波器及重采樣中抽取因子的設置以及輸出方式設置等。

數據處理模塊可完成對最后數據標志位的處理以及必要的數據合并或分解處理,FIFO存儲控制模塊則可產生FIFO工作的控制時序。

3.4 緩存及接口

因為PCI總線接口數據傳輸效率非常高,而A/D采集數據的效率較低,所以,為了實現數據的高速傳輸,本設計采用IDT公司的FIFO芯片IDT72T72105來實現板上緩存,采樣后的數據經過緩存后,再由PCI總線接口控制器讀取,這樣可以保證數據的實時性傳輸。

實現PCI總線接口的方式有兩種,一種是采用專用PCI接口芯片,但專用芯片價格昂貴、功能繁雜、不能靈活配置、不利于系統的升級優化;另一種是進行基于IP核的FPGA設計,這種方法多用在設計者只需要用PCI接口的部分功能的場合。本設計采用第二種方式來實現PCI總線的數據傳輸,利用FPGA進行PCL總線設計,可以在單片FPGA中同時完成PCI接口和用戶邏輯的設計,該方法可縮減成本,而且設計靈活,集成度高,并可減少資源浪費。

4 實驗結果

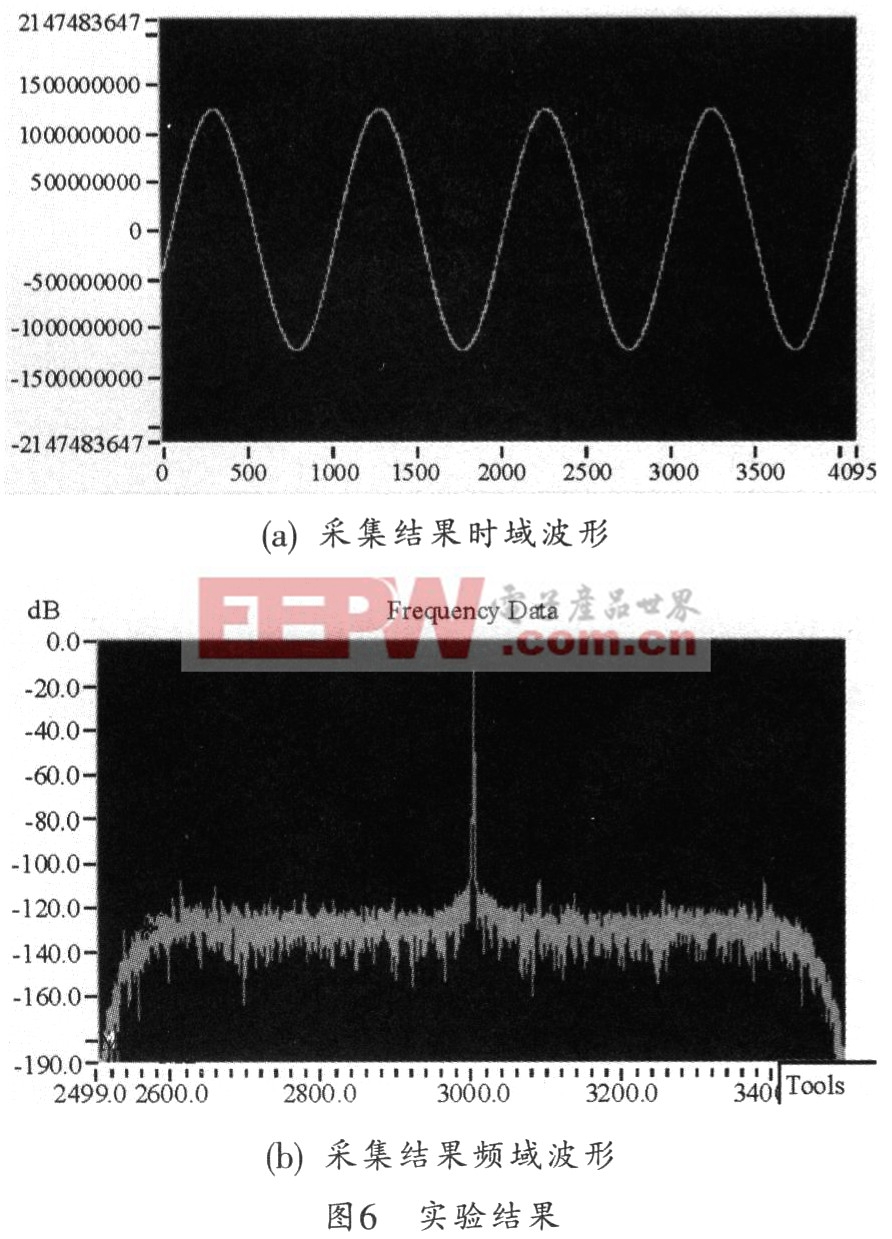

本系統密集度高,芯片多為BGA封裝,故在布局時應注意將數字部分和模擬部分盡量分開,以避免數字電路通過線間分布電容對模擬電路產生干擾。另外,在應用場所周圍,如存在強干擾電磁場,還應在模擬電路部分加屏蔽措施。圖6所示是用100 MHz內部時鐘來對頻率為3MHz的正弦信號進行采樣,同時設置DDC本振頻率為2.999 MHz,5階差分梳妝濾波器抽取因子為25 (即總抽取因子為25x2x2=100)所獲得的波形及頻譜圖。

若系統時鐘為100 MHz,總抽取率為100,則系統對下變頻信號的采樣率為l MHz,而數字下變頻后的信號頻率為l kHz。根據Nyquist采樣定理,使用1 MHz的采樣率對l kHz的信號進行采樣,完全可以不失真地恢復原始信號,即信號應當出現在1kHz處。但是,為了能讓用戶直觀地從頻譜圖上讀出原始信號的頻率,可以在頻譜圖上顯示差頻頻率加上本振頻率后的信號頻譜圖,故本該出現在1 kHz處的信號,搬移到了3 MHz處,圖中的信號出現在了3000.015 kHz處,這與理論分析一致。

5 結束語

本系統除了ADC及電源轉換芯片外,全部采用BGA封裝,這種設計使得整個系統體積小巧,集成度高。系統的數字下變頻功能完全通過FPGA對數字下變頻器件的重新配置來實現,因而提高了系統的靈活性,解決了傳統數字接收機的缺點,體現了軟件無線電技術的優越性。

評論