一種用于飛行器下傳數據處理的高速數據采集存儲系

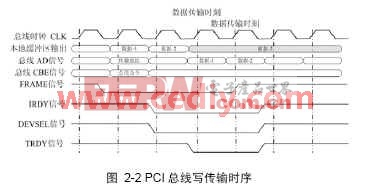

一個典型的PCI總線上的寫數據傳輸時序如圖2-2中所示。首先用于傳輸的數據必須要提前從本地的緩沖區(qū)中讀出,然后出現在總線AD信號線上,當IRDY信號和TRDY信號同時有效時(為低電平時),被目標設備獲取。當傳輸結束時,最后一個從本地緩沖區(qū)中預讀出的數據(如圖中陰影的數據3),并不會被傳輸到目標設備。而本地的緩沖區(qū)控制模塊會認為數據已經傳輸,這時如果不采取措施就會導致數據丟失。

本文引用地址:http://www.104case.com/article/195557.htm

在傳輸結束的時候,PCI總線傳輸狀態(tài)機會切換到備份數據的狀態(tài),在這個狀態(tài)下,緩沖區(qū)的控制模塊會檢測是否存在已經讀出而未傳輸的數據,如果存在這樣的情況,控制模塊則采取措施防止數據丟失。對于雙口RAM這種存儲結構而言,數據讀出以后,只要沒有在同一地址寫入數據,那么數據是不會丟失的,因此要實現前面的功能只需要簡單的修改一下讀指針目前指向的地址就可以實現。

2.4 傳輸控制模塊的設計

傳輸控制模塊的核心是一個傳輸控制狀態(tài)機。它通過檢測存儲緩沖區(qū)的情況,來控制傳輸的進行。當輸入緩沖區(qū)中數據存儲滿或輸出緩沖區(qū)空以后,自動請求一次數據傳輸,由此保證數據流的連續(xù)。

3 驅動與應用程序的開發(fā)

驅動程序的開發(fā)是采用標準的WDM(Windows Driver Model)設備驅動程序模型,利用DriverStudio的驅動程序開發(fā)工具包來進行開發(fā)的。關于WDM的驅動程序模型,限于篇幅的原因就不作詳細的介紹。

一個典型的數據傳輸過程是這樣進行的。首先驅動程序完成設備的初始化,如在內存中開辟緩沖區(qū),硬件設備的初始化等等。完成初始化以后硬件就處于等待傳輸的狀態(tài)。當用戶通過應用程序發(fā)出傳輸數據的指令以后,驅動程序處理這一請求,并對硬件發(fā)出指令開始數據傳輸。由于數據傳輸的時間可能比較長,所以應用程序采用多線程的設計,傳輸線程會等待驅動程序在傳輸結束時發(fā)出的信號,而同時應用程序還能完成與用戶的交互工作。當傳輸結束后,驅動程序向硬件寫入停止指令,中止傳輸,并向應用程序發(fā)出傳輸結束信號。驅動程序對應用程序的通信是通過創(chuàng)建Win32事件來實現通信的。

4 設計的仿真和驗證

為了驗證設計的正確性,首先需要對設計進行邏輯功能仿真。為了驗證設計是否能正常的工作在PCI總線上,那么就需要仿真PCI總線上的各種總線事務,驗證設計是否能響應各種總線命令。仿真是在Xilinx公司提供的PCI總線接口仿真實例的基礎上實現的。按照PCI總線規(guī)范設計了一個簡單的總線仲裁器,用來仿真主設備申請總線占用的過程。此外還設計了一個PCI總線上的從設備,用來仿真主設備與從設備之間的數據傳輸過程。此外還仿真了總線上對設備的自動配置過程。通過觀察仿真波形圖,發(fā)現設計完全滿足PCI總線的數據傳輸規(guī)范,而且數據傳輸的結果正確。

在仿真驗證正確的基礎上,將設計實現于Xilinx公司型號為virtexII2v1000-fg456-5的FPGA中。將數據接口卡安裝于測試計算機上,利用數據接口卡的自回路數據傳輸功能以及單向輸入輸出功能,對系統(tǒng)進行了驗證和性能測試,結果如表格1中所示。

從結果可以看出,當輸入輸出速率保持在160Mbps以下時,可以保證自身回路數據傳輸無錯進行,但是當速率提高到200Mbps以后,傳輸就會出現數據丟失,導致接收的數據與發(fā)送數據不一致。因此,為了保證數據的無錯傳輸,自身回路數據傳輸測試速率應該不高于160Mbps。

單向輸入輸出測試時,當輸入速率或者輸出速率小于300Mbps,系統(tǒng)的功能是完全正確的,而當工作于400Mbps的時候,則會出現數據丟失的情況。與自身回路傳輸測試的數據比較可以看出,當在自身回路數據傳輸測試速率為200Mbps的時候,由于此時系統(tǒng)接收和輸出同時進行,共同分時使用總線,此時相當于單獨接收或者單獨輸出測試時400Mbps的傳輸速率。兩次測試結果的一致性也說明了測試的可靠性。

5 結語

通過對系統(tǒng)的測試驗證,證明了本設計能夠完全滿足高速實時數據流對數據采集存儲系統(tǒng)的要求。為了方便以后進一步的工作,在測試時也對緩沖區(qū)大小和傳輸速率之間的關系進行了簡單的測試。將緩沖區(qū)大小從8KB改變到16KB以后,傳輸速率只是稍微有些提高,對性能的改善十分不明顯。結果說明簡單的擴大硬件緩沖區(qū)并不會帶來數據傳輸速率的明顯改觀,同時還會占用FPGA內部寶貴的RAM資源。究其原因在于,數據傳輸速率主要受到32位/33MHzPCI總線帶寬自身的限制,以及硬盤讀寫的峰值速率的限制,而并不是緩沖區(qū)大小的影響。可以預見如果采用64位/66MHz的PCI總線并采用更多的磁盤來構成RAID磁盤陣列以提高磁盤讀寫速率,那么整體的性能會有很大的提升。

評論