通用線陣CCD采集系統設計

2.2 通用驅動采集板

通用驅動采集板由A/D轉換、FPGA(通用CCD驅動器模塊和16In8Out異步FIFO模塊)、USB 3部分組成。A/D轉換部分完成系統的A/D轉換;FPGA部分完成系統的CCD驅動、數據采集、CDS實現;USB部分完成數據的傳輸。

2.2.1 A/D轉換部分

系統需采集多種CCD并實現CDS,而且系統主要由USB供電,這就要求A/D轉換速度快,供電電壓低,最好參考電壓內置。AD9235-40屬于12位、40 MS/s模數轉換器系列,采用3 V單電源供電,該系列均內置一個高性能采樣保持放大器(SHA)和基準電壓源。AD923540采用多級差分流水線架構,內置輸出糾錯邏輯,在40 MSP/S數據速率時可提供12位精度,并保證在整個工作溫度范圍內無失碼。

FPGA中采集信號發生器提供A/D采集時鐘,同時也控制FIFO和CCD驅動器。A/D采樣速率不再受數據傳輸和采集制約,采樣速率完全和CCD速度匹配。并可實現1幀內1個像元的雙采樣,從而實現CDS。

2.2.2 FPGA部分的通用CCD驅動器模塊

由于不同生產商的CCD器件的驅動時序往往差別很大,因此需針對每種CCD器件編制其CCD驅動器模塊。驅動時鐘和采集脈沖由分頻器和采集信號發生器提供,如圖2所示。

CCD驅動器輸入信號由兩路驅動時鐘和積分時間控制信號INT組成;輸出信號由幀同步信號FS和CCD Driver信號組成。不同的CCD驅動器模塊僅CCD Driver信號有所不同,其他接口一樣。在改變CCD時只需替換CCD驅動器模塊即可。

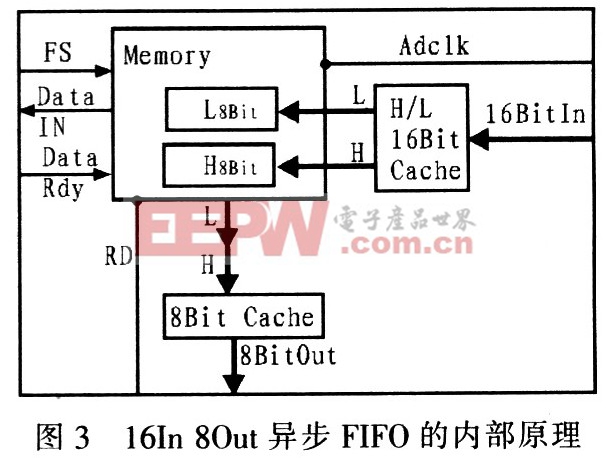

2.2. 3 FPGA部分的16In8Out異步FIFO

FIFO用于暫存A/D轉換的信號。待存滿1幀并且USB塊傳輸空閑后,將FIFO中的1幀數據通過快速塊傳輸上傳至計算機。1幀的像元個數由CCD驅動模塊提供的FS信號決定。FIFO內的存儲空間為192 Kb。滿足線陣CCD和小型面陣CCD的數據存儲需求。圖3為16In8Out異步FIFO的內部原理圖。

評論