基于PCIe總線的超高速信號采集卡的設計

4.2 系統(tǒng)采集時序控制

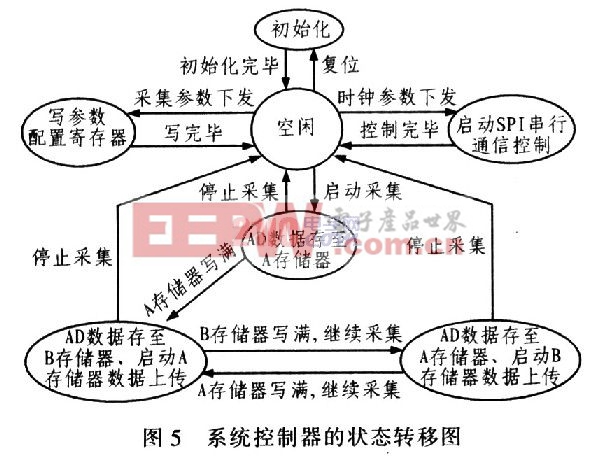

系統(tǒng)控制模塊完成采集數據上傳、主機命令的下發(fā)和執(zhí)行:系統(tǒng)控制采用有限狀態(tài)機的控制方式,如圖5所示。當系統(tǒng)上電后控制器默認進入初始化狀態(tài),完成默認參數的配置,包括采樣頻率、采樣深度、觸發(fā)方式、時鐘源的選擇、模擬輸入的量程和耦合方式等,初始化執(zhí)行完畢后進入空閑狀態(tài),等待接收主機命令和執(zhí)行操作;當接收到啟動采集的命令后,控制器首先將AD輸入的數據總線掛接在內存A數據總線上,并啟動內存A的DDR2控制器執(zhí)行寫操作;當內存A存儲到軟件設定的深度或存滿時,切換AD輸入的數據總線掛接在內存B數據總線上,啟動內存B的DDR2控制器執(zhí)行寫入操作,同時通過DMA中斷通知主機,等待主機上傳內存A中的數據;如此反復循環(huán)工作,直到收到主機停止采集

的命令再返回到空閑狀態(tài)。本文引用地址:http://www.104case.com/article/195369.htm

5 結束語

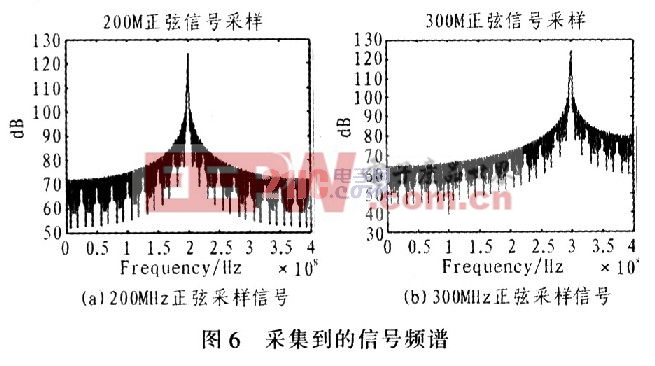

本文介紹了基于PCIe高速串行總線和FPGA控制器的超高速信號采集卡的設計技術,實現(xiàn)了不間斷采樣和連續(xù)傳輸等關鍵技術。采集到的信號頻譜見圖6。該采集卡已應用于某雷達偵察和干擾系統(tǒng),取得了良好的效果,具有重要的實用價值。

評論