等精度頻率計的實現

等精度測頻的原理圖如圖2所示。圖中,預置軟件閘門信號GATE是由FPGA的定時模塊產生,GATE的時間寬度對測頻精度的影響較少,故可以在較大的范圍內選擇。這里選擇預置閘門信號的長度為1s。圖中的CNT1和CNT2是2個可控的32位高速計數器,CNT1_ENA和CNT2_ENA分別是其計數使能端,基準頻率信號f0從CNT1_CLK輸入,待測信號fx從CNT2的時鐘輸入端CONT2_CLK輸入,并將fx接到D觸發器的clk端。測量時,由FPGA的定時模塊產生預置的GATE信號,在GATE為高電平,并且fx的上升沿時,啟動2個計數器,分別對被測信號和基準信號計數,關閉計數閘門必須滿足,GATE為低電平,且在fx的上升沿。若在一次實際閘門時間Tx中,計數器對被測信號的計數值為Nx,對標準信號的計數值為N0,而標準信號的頻率為f0,則被測信號的頻率為fx,則fx=(N0/Ns)f0。圖2中的所有功能都在FPGA端實現。本文引用地址:http://www.104case.com/article/195309.htm

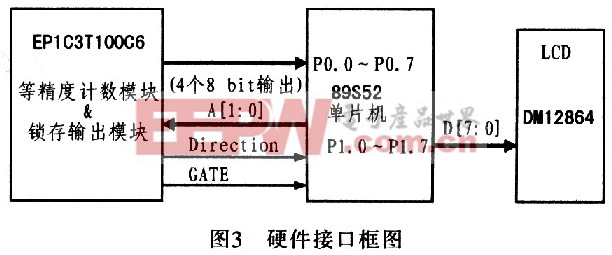

圖2所示的單元完成了等精度測頻的核心部分,在實際應用中多數時候需要將測量的結果通過顯示設備進行顯示。從圖2可以看出本設計由于設計了鎖存單元,將計數結果和一些控制信號進行了鎖存處理,便于與單片機或者其他的單片機(MCU)相連,因此在該FPGA實現的核心單元基礎上連接MCU,容易實現計數值到實際頻率值以及相應的周期值之間的轉換,并通過MCU控制顯示設備將最終需要顯示的結果信息進行顯示。FPGA器件與單片機硬件接口電路框圖如圖3所示。圖3中的等精度頻率測量模塊和鎖存模塊都由Altera公司的FPGA器件EP1C3T100C6實現,等精度計數模塊的輸出結果為2個32 bit的數據,為了方便與單片機連接,該2個32 bit數據由在FPGA器件內部的鎖存器分8次鎖存輸出,單片機每次讀取8 bit,連續讀取8次即可,讀取的Nx和N0的計數值經過單片機按照等精度頻率計算公式換算成實際頻率值,最后通過DM12864進行顯示。

3 測量結果的誤差分析

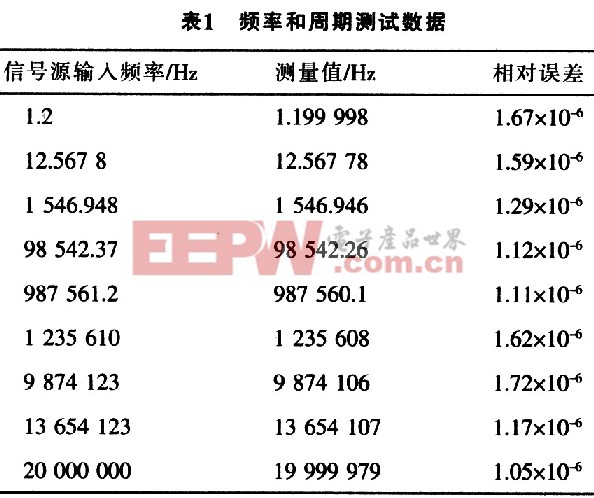

采用高精度信號源輸出不同頻率的正弦波信號,經過信號調理電路,整形得到的方波信號提供給FPGA進行計數測量,將測量結果與高精度信號源輸出的頻率相比較,計算其誤差,如表1所示。

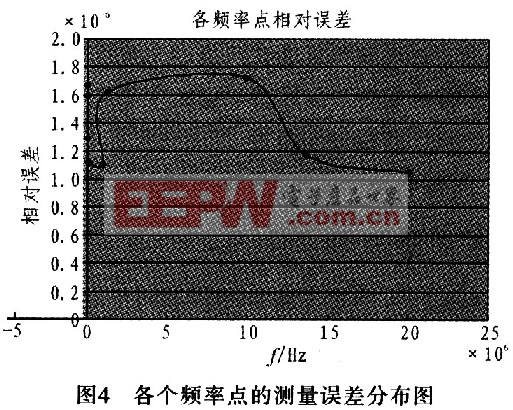

表l給出了各種頻率的測量結果和誤差。結果顯示,本設計在1Hz~20MHz全范圍內的測量誤差小于2×10-6。從圖4可以看出測量結果的誤差分布在同一個數量級附近,達到了等精度測量的目的。在實際測試中發現,如果提高系統晶振的頻率或者提高晶振的精度級別,頻率測量的誤差還會進一步降低。

4 結束語

詳細介紹了等精度測量的原理,并給出等精度測量的思想在FPGA上實現的方法。測試結果表明該等精度測量方案誤差非常小,在測量范圍內誤差恒定。該設計方案對測量頻率實現設計具有一定的借鑒。

評論