便攜式心電信號采集電路設計

3.6 主放大電路

為滿足A/D轉換器對信號幅度的要求,兩級放大器共放大l 000倍左右,一級放大電路放大倍數為8倍,所以二級放大倍數設計為125倍。從整個電路集成度和器件性價比考慮,這里選用TL064。該器件內部集成4個運放,每個放大器的功耗只有6 mW,符合便攜產品的要求,且價格較低,可減少實驗和生產成本。放大電路采用簡單的反饋放大電路,調節電阻參數即可。本文引用地址:http://www.104case.com/article/195229.htm

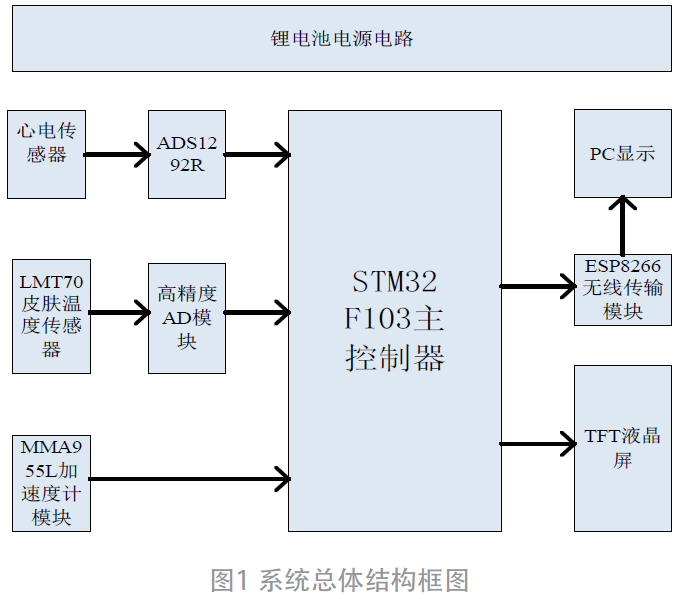

4 數字處理部分

4.1 A/D轉換

已放大的模擬信號要實現存儲和顯示,需要轉化為數字信號,因此要完成A/D轉換。A/D轉換首先解決采樣率和A/D轉換器的選型。

采樣率,美國心臟學會推薦的采樣率為500 Hz,但實際中不同應用有不同的采樣率,一般在125~1 000 Hz之間,監護時多采用200 Hz或250 Hz,輔助分析時多用400~500 Hz,而心電HOLTER一般取125~200 Hz。采樣精度為10 bit或12 bit。

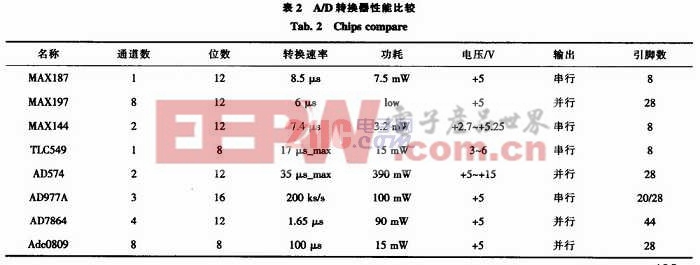

對于A/D轉換器的選型,要根據電路形式、轉換速率、通道數目、采樣精度、功耗大小、供電電壓等因素綜合考慮,選出性價比較高的轉換器。在確定器件前,表2給出備選的幾款A/D轉換器的比較結果。

通過表2和實際項目的要求,最終確定使用MAXl97,其采樣位數,轉換速率,功耗,體積等方面均符合心電A/D轉換的要求。另外,該轉換器有8個模擬信號輸入端,可采集8路模擬信號,符合心電設備多導聯的要求。

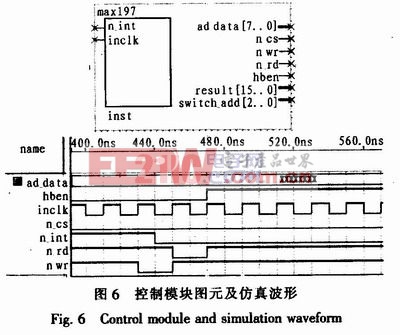

控制模塊使用VHDL語言編程實現,根據MAXl97的時序圖,利用有限狀態機的方法實現控制模塊。具體內容是根據A/D轉換的進程,將轉換過程分為5個狀態:1)為初始化,寫入讀寫信號及通道選擇和轉換電壓范圍等控制字;2)為啟動轉換,在時鐘控制下,輸出信號使得A/D轉換器開始轉換;3)為判斷轉換是否完成,若未完成繼續轉換,若完成跳入下一個狀態;4)為讀低8位,給轉換結束標志信號hben賦值O,讀出已經轉換完的低8位;5)為讀高4位,給hben賦值1,讀出高4位。

圖6是根據上述狀態機VHDL語言實現后生成的圖元符號及控制模塊的仿真波形。從仿真波形上可以看出,該模塊符合A/D轉換器的時序要求,能在功能上實現對A/D轉換器的控制,得到所需要的數字信號。

A/D轉換器的控制信號由FPGA提供。基于FPGA平臺搭建一個A/D轉換的控制模塊。選擇FPGA做控制平臺,是由于FPGA有著豐富的可編程邏輯資源,利用這些資源可以實現心電設備中的控制存儲、顯示、按鍵、通信等其他模塊。這些模塊都在FPGA上完成就構成了片上系統,使得設備體積和可靠性都有了很大程度上的提高。選擇FPGA也是出于項目整體方案的考慮。

5 結束語

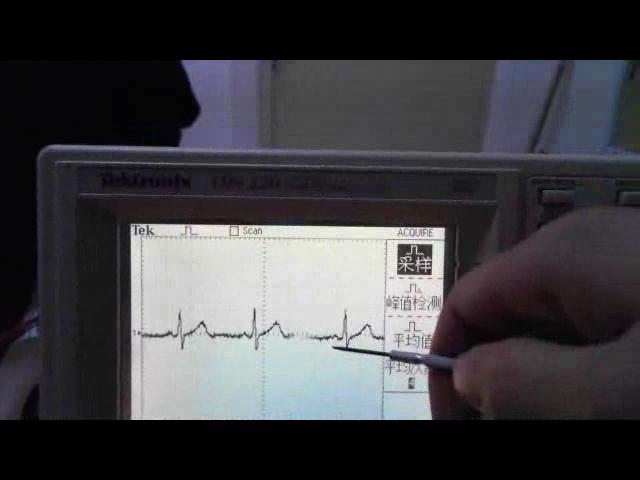

在項目的要求下,通過分析心電信號的特點,從幅值,頻率,噪聲等各方面有針對性的設計了心電采集電路,并對每一環節都做了仿真和測試,最大程度上精簡電路,滿足便攜式設備對體積的要求,同時保持較高的性能,能有效采集到心電信號。對采集到的心電信號,用FP-GA控制A/D轉換模塊,得到數字信號,以便后續的數字處理。另外,由于FPGA的豐富可編程資源,可以在這個采集系統基礎上升級為診斷并顯示的系統。

評論