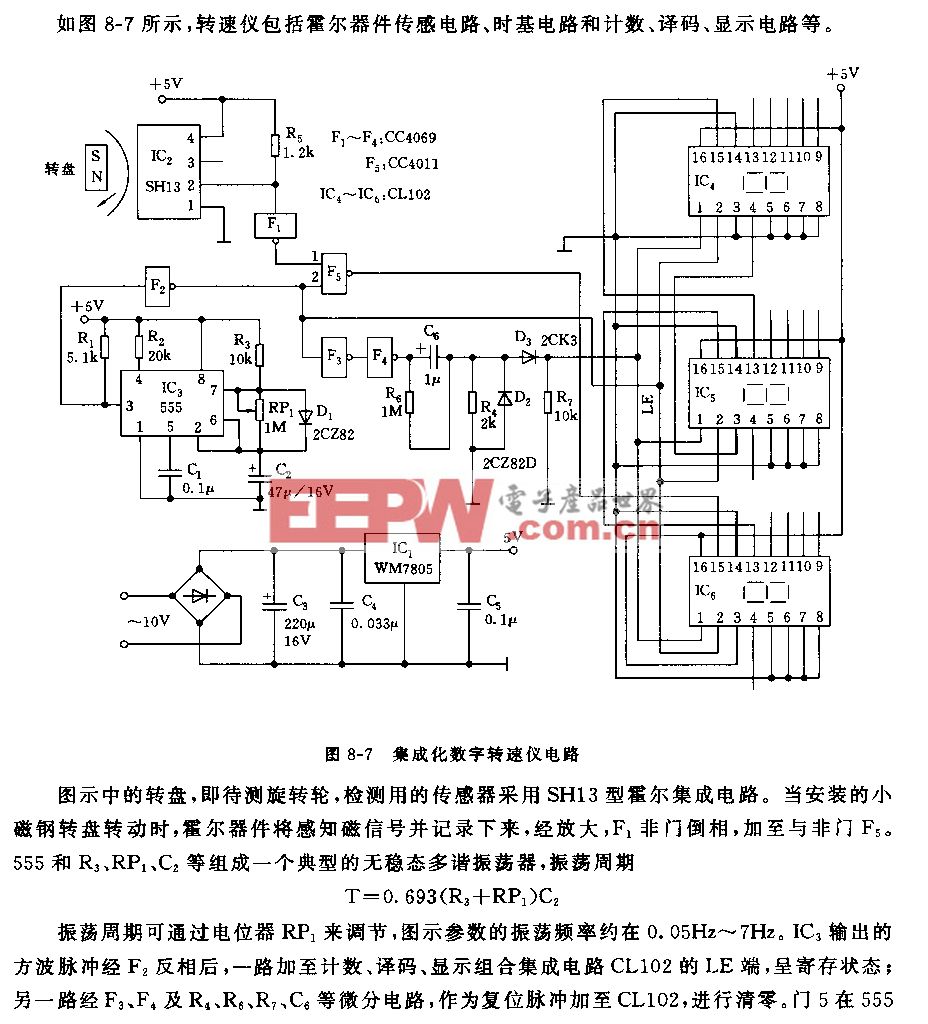

一種高速化和集成化的數(shù)據(jù)采集系統(tǒng)的設(shè)計

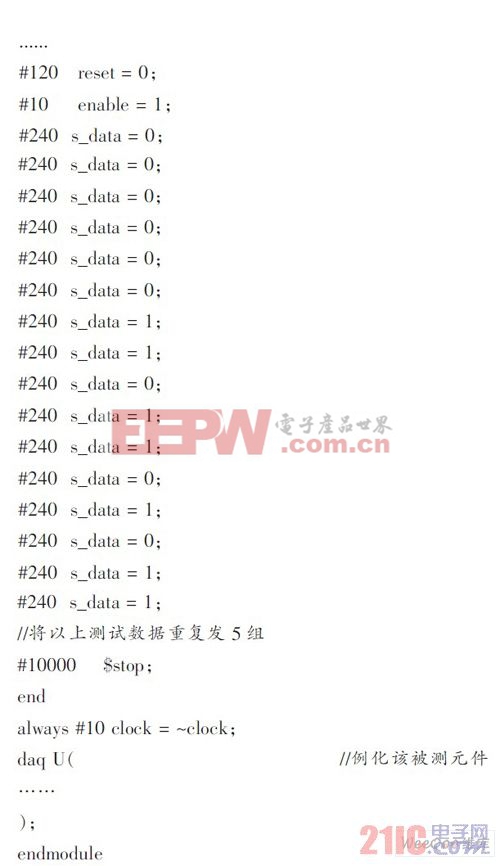

目前需要對adc.v模塊進行功能仿真,以此驗證該模塊的功能的正確性。仿真測試的方法就是給adc.v這個模塊的s_data數(shù)據(jù)輸入端,即A/D芯片的串行數(shù)據(jù)的輸出端,加載一組測試數(shù)據(jù),每16個為一組測試數(shù)據(jù),模擬在真實環(huán)境下從A/D芯片讀取出來的二進制數(shù)據(jù),然后在adc.v模塊的輸出端,即并行的16位寬的data_out端口觀察是否與給定的測試數(shù)據(jù)相一致。假如一致,則模塊的功能是正確的。假如有個別位的數(shù)據(jù)不一致,則需要檢查模塊的代碼是否存在問題。在編輯器中編寫Testbench程序如下(非關(guān)鍵的程序限于篇幅,就省略了):

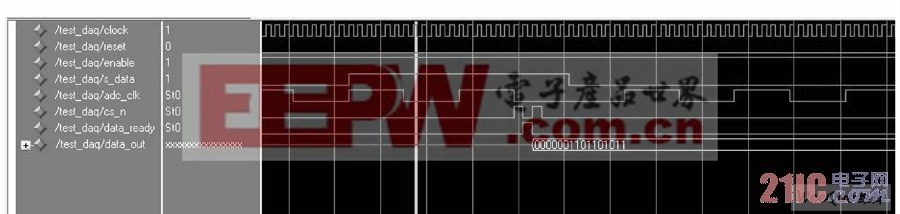

由上面的程序可以看見,給s_data端加載的一組16位二進制數(shù)據(jù)為“0000-0011_0110_1011”。在ModelSim環(huán)境下,將待測試的文件與該測試文件放在同一個工程下,設(shè)置好相關(guān)參數(shù)后運行仿真可以得到如下仿真波形,如圖7所示。

圖7 仿真波形

由圖7可見,從data_out這個并行的數(shù)據(jù)端口讀出的數(shù)據(jù)正是在Testbench仿真測試文件中給定的那一組測試數(shù)據(jù),仿真得到的結(jié)果是正確的。

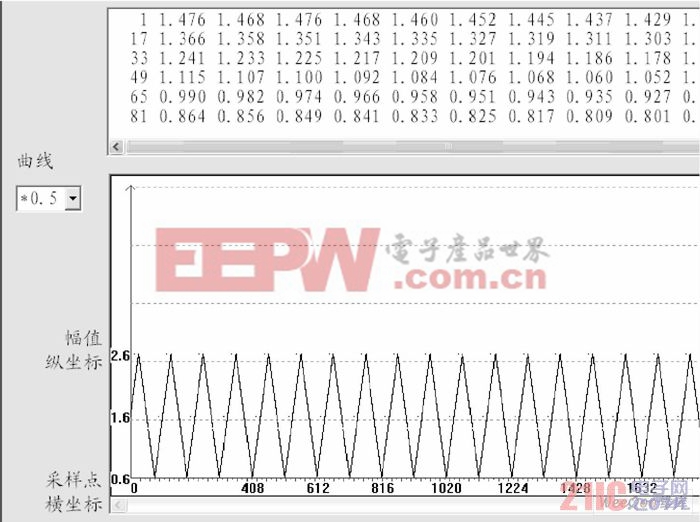

在FPGA控制A/D芯片接口的軟件設(shè)計中,是通過FPGA內(nèi)部的邏輯電路實現(xiàn)了分頻,并將分頻后的信號作為A/D芯片工作的采樣時鐘,經(jīng)過測試,得知A/D芯片的采樣頻率為1.08 MHz,通過信號發(fā)生器,將輸入的模擬信號設(shè)為10 kHz、幅度為3 V的正弦波,采樣轉(zhuǎn)換后的數(shù)據(jù)上傳到上位機中,顯示的波形如圖8所示。

圖8 10KHZ信號輸入時得到的波形

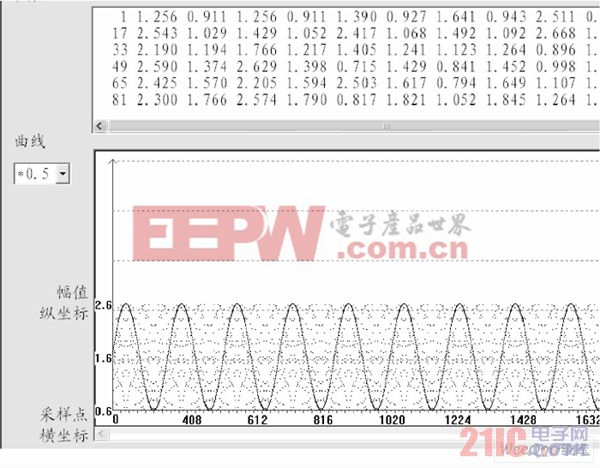

在同等條件下,把輸入的模擬信號的頻率調(diào)整為5 kHz。A/D芯片的采樣頻率仍然為1.08 MHz。得到的顯示波形如圖9所示。

圖9 5 kHz信號輸入時得到的波形

由圖8和圖9可知,在對模擬信號采樣時,當(dāng)采樣率不變時,輸入模擬信號的頻率越低,相對地就提高了采樣點、減小了采樣間隔,在圖形中就越能體現(xiàn)出原始模擬信號的信息,得到的波形就更加的理想。

5 結(jié)束語

本文在研究了FPGA和USB2.0技術(shù)的基礎(chǔ)上,提出了數(shù)據(jù)采集系統(tǒng)的總體設(shè)計方案,以FPGA和USB2.0為技術(shù)核心,設(shè)計了硬件電路和軟件代碼并在ModelSim環(huán)境下通過了仿真測試。該系統(tǒng)不僅能夠?qū)崿F(xiàn)一般用途的數(shù)據(jù)采集,還實現(xiàn)了系統(tǒng)的高速化、集成化和低功耗工作,為便攜化數(shù)據(jù)采集系統(tǒng)提供了一種設(shè)計思路。

評論