多總線融合式通用自動測試系統設計

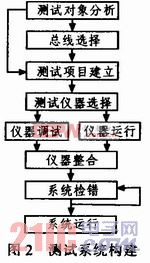

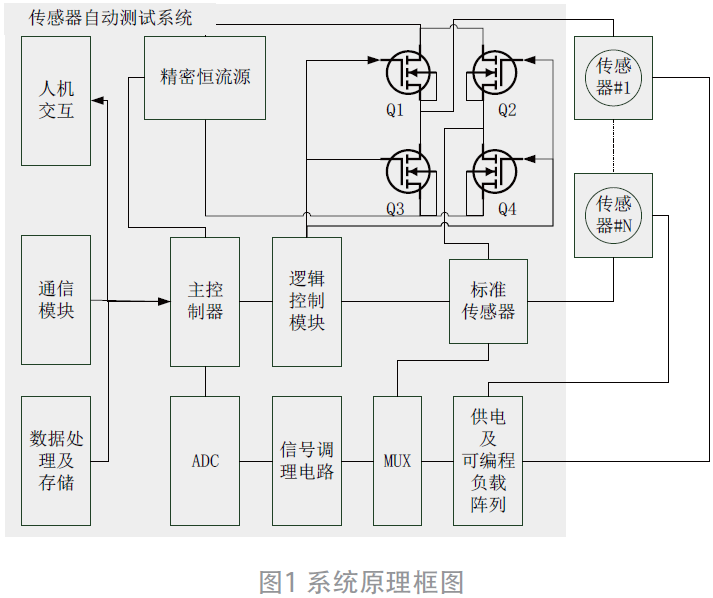

該基本型能夠適應多種測試需求,從以上各方案中可以得出在以此基本型建立自動測試系統時,可加入總線,也可不配置總線建立小型測試系統,基于此基本型建立測試系統方法如圖2所示。本文引用地址:http://www.104case.com/article/195049.htm

1.3 轉接口設計

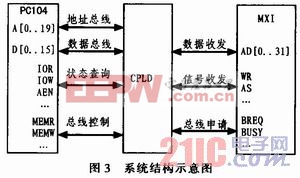

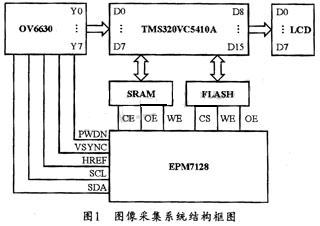

要實現PC/104主機與外界的通訊,轉接口的設計是其中非常重要的環節之一。而在本方案中PC/104總線轉MXI總線接口的設計好壞是關乎著整個系統能否實現高速測試的關鍵。復雜可編程邏輯器件(CPLD)幾乎適用于所有的陣列和各種規模的數字集成電路,它以其編程方便、集成度高、速度快、價格低等特點越來越受到設計者的歡迎。轉接口的設計采用CPLD即可完成要求。接口設計方案如圖3所示。

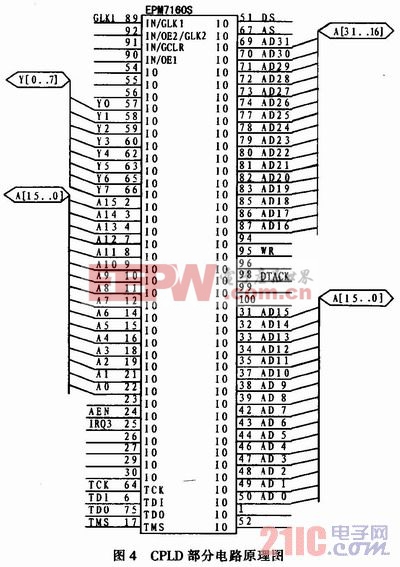

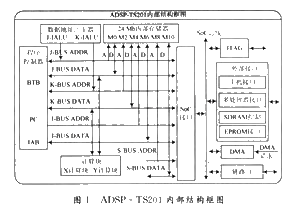

通過對PC/104總線和所選總線的時序、信號、地址、數據等方面的需求分析,用CPLD設計接口模塊,實現總線握手和數據傳輸功能。C-PLD部分電路原理如圖4所示。

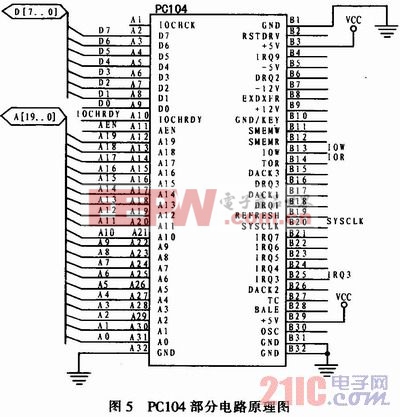

PC/104使用的總線資源主要是I/O控制和中斷,具體信號如下:A[0..19]是PC/104的10位地址總線;D[0..7]是PC/104的8位雙向數據總線;IOR,IOW分別是總線I/O端口讀、寫信號;AEN是允許DMA控制地址總線、數據總線和讀寫命令線進行DMA傳輸以及對存儲器和I/O設備的讀寫;IOCHRDY是I/O就緒信號,I/O通道就緒為高;SYSCLK是系統時鐘信號,使系統與外部設備保持同步;IRQ3是中斷信號。PC104部分電路原理如圖5所示。

1)數據傳輸(PC/104→MXI) PC/104需要傳送數據時,PC/104置位AEN信號,通過發送地址與數據總線向CPLD發送數據,此時IOW引腳置低電平(有效)。當CPLD接收到正確數據后,驅動MXIbus的地址選通信號AS,獲取地址信息后,再驅動MXI的數據選通信號DS,置位讀寫信號WR取走數據,通過MXI的應答信號DTACK來判斷數據是否傳輸完畢,完畢則發送下一個數據,MXIbus采用的是地址數據總線復用形式。

2)數據傳輸(MXI→PC/104) 當MXI向CPLD傳送數據時,置位AS,驅動數據選通信號DS,并且WR有效,發送數據。CPLD收到數據后,通過IRQ3向PC/104發送中斷申請,PC/104收到中斷信號后,首先置位AEN,然后IOR變低電平,從CPLD寄存器口地址讀取數據。

評論