基于CS5451A多路同步數據采集系統設計

2 異步FIFO的設計

本設計中所用的FPGA芯片是XILINX公司的XC3S100E,XC3S100E是XILINX SPARTAN3E系列一款最低容量的FPGA芯片,此系列FPGA利用90 nm工藝實現低成本高容量的需求,XC3S100E具有以下資源:

1)有2160個邏輯單元;

2)具有RAM資源87 kB(其中BLOCK RAM 72 kB,分布式RAM 15 kB);

3)具有兩個DCM;

4)具有4個乘法器;

5)可以實現FIFO等多個IP核。

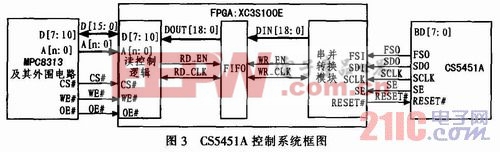

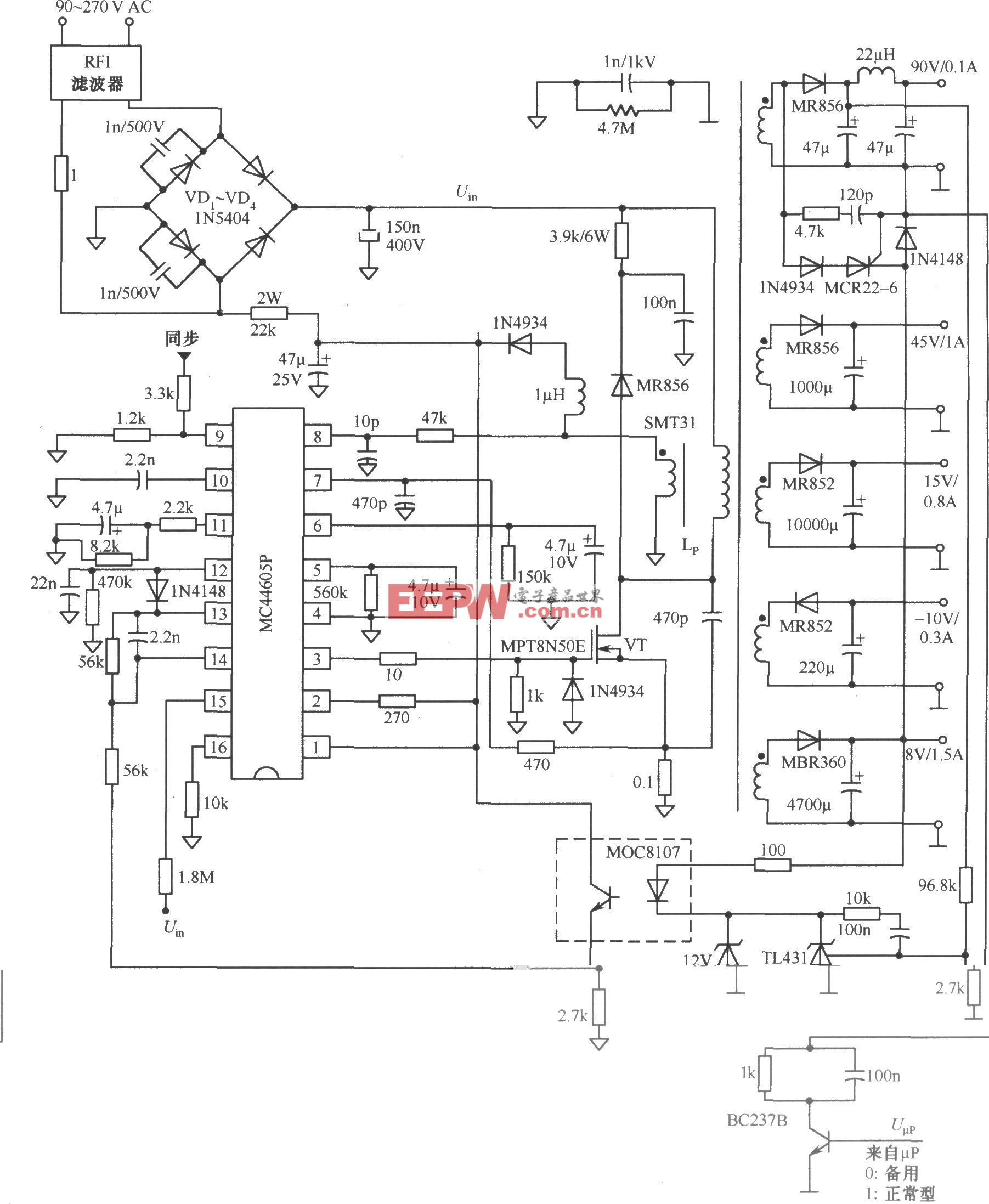

在XILINX ISE10.1集成開發工具下,很容易利用XININX免費IP核實現一個異步FIFO。異步FIFO是在兩個相互獨立的時鐘域下,數據在一個時鐘域寫入FIFO,而在另外一個時鐘域下又從該FIFO中將數據讀出。CS5451A控制系統框圖如圖3所示,異步FIFO和串并轉換模塊作為CPU和CS5451A之間的橋梁,由串并轉換模塊將ADC輸出的串行數據轉換成19位的并行數據(其中16位為數據,3位為采樣通道號0~5)寫入異步FIFO,這樣FIFO就成為CPU前端的一個緩沖器。每接收完成1幀數據便向CPU發出一個中斷信號,通知CPU讀取FIFO中的數據。本文引用地址:http://www.104case.com/article/195006.htm

異步FIFO IP核的參數指標直接影響FIFO的讀出速度,首先,FIFO的讀出速度快能夠減少CPU的開銷,這樣CPU可以有更多的時間干實時性更高的任務。其次,FIFO的存儲深度要適宜,深度過大造成資源的浪費,深度過小會造成控制復雜,這樣將占用更多的資源。本設計中的異步FIFO是利用ISE10.1中的參數化的IP核在XC3S100E芯片的實現。由于1個CS5451A芯片共有6通道ADC,ADC的分辨率為16位,考慮到數據的可靠性,每一個ADC通道的數據包括通道號(占3位),考慮到有的時候可能CPU不能及時的讀走數據,所以在參數化的FIFO設計中選擇FIFO深度為64,寬度為19位。

3 基于FPGA串并轉換模塊的設計

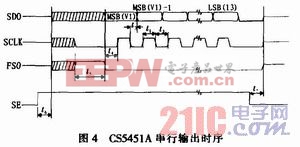

CS5451A通過一個Master模式的串行接口輸出采樣數據,輸出數據通過SDO輸出,SCLK為輸出串行時鐘,CS5451A串行輸出時序圖如圖4所示,FSO是幀同步信號,表示一幀數據的開始,如果SE信號為高電平,這3個信號就有效,如果為低電平,3個信號都為高阻狀態,在本設計中,CPU初始化后把SE設置成高電平。正常情況下,FSO信號為低電平,當有一幀數據要輸出的時候,FSO信號變為高電平,高電平寬度為1個SCLK周期。當沒有數據輸出的時候,SCLK為低電平,FSO從高電平變為低電平后,SCLK時鐘信號有效,數據在上升沿輸出,SCLK共持續16x6個周期,數據串行輸出時,MSB最先輸出。

評論