基于MC8051內(nèi)核的便攜幅頻特性測試儀設計

在現(xiàn)代電力電子系統(tǒng)中,隨著內(nèi)場測試和外場維護工作量的增加,對目前通用的測試儀器也提出了新的要求,研制低成本、體積小的便攜式幅頻特性測試儀具有深遠的現(xiàn)實意義。目前,結合新型微處理器芯片進行幅頻特性測試儀的研制主要有三種技術途徑:(1)采用單片機作為主控芯片,通過軟件編程方式實現(xiàn)部分硬件功能,這種方案可以有效降低系統(tǒng)的復雜度,但在實時性上不盡人意。(2)應用可編程邏輯器件(如FPGA)進行設計可以有效解決高速數(shù)據(jù)流的實時處理問題,但在人機界面的設計中具有較大困難。(3)采用單片機與FPGA芯片結合的方式,通過外部總線連接和數(shù)據(jù)傳輸協(xié)議的設計,使得系統(tǒng)兼具兩者的優(yōu)勢,從而成為設計人員首選的主流方案。

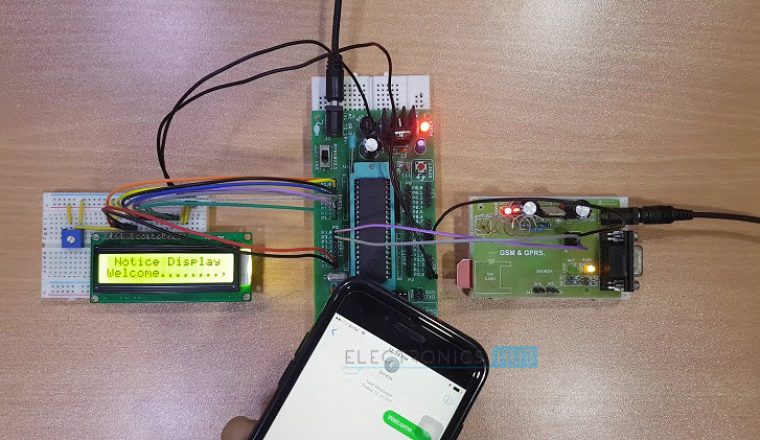

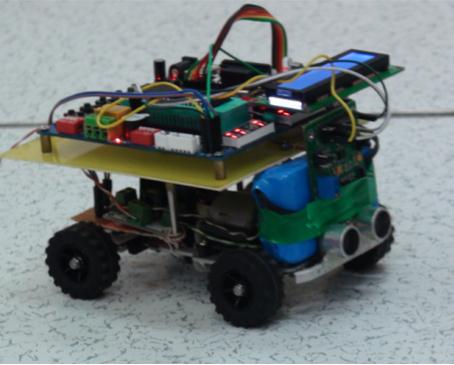

現(xiàn)代EDA(Electronic Design Automation)技術的發(fā)展和大規(guī)模FPGA器件的推出,使得在單片F(xiàn)PGA芯片中進行嵌入式8051 IP核設計成為可能。應用現(xiàn)代EDA技術,以FPGA器件為硬件平臺,使用VHDL語言編程,可以實現(xiàn)與MCS-51系列單片機指令系統(tǒng)完全兼容的微控制器芯片IP(Intellectual Property)核[1]。本文以此為基礎,提出了幅頻特性測試儀設計的新途徑。系統(tǒng)以FPGA為核心采集處理模塊,以Oregano公司開發(fā)的嵌入式MC8051內(nèi)核(以下簡稱51內(nèi)核)為顯示控制核心,通過FPGA內(nèi)部的正弦查找表IP核外加D/A模塊的思想產(chǎn)生系統(tǒng)需要的掃頻信號源,同時采用2.4英寸TFT彩屏液晶顯示器進行人機界面設計,實現(xiàn)了便攜式幅頻特性測試儀的基本功能。該儀器具有小型化、頻帶寬、操作簡單、測量精確度高、界面顯示友好等優(yōu)點,具有廣闊的應用空間。

1 系統(tǒng)組成與工作原理

1.1 系統(tǒng)組成

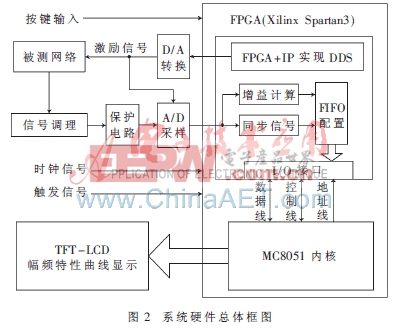

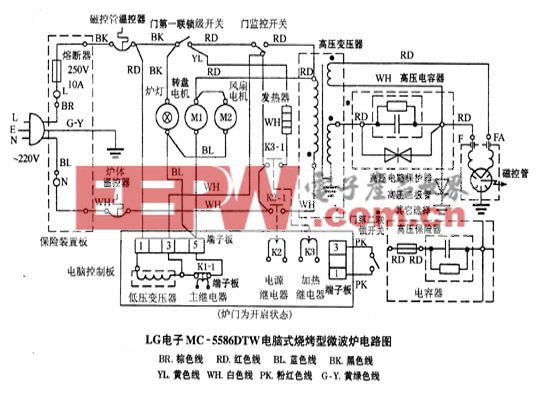

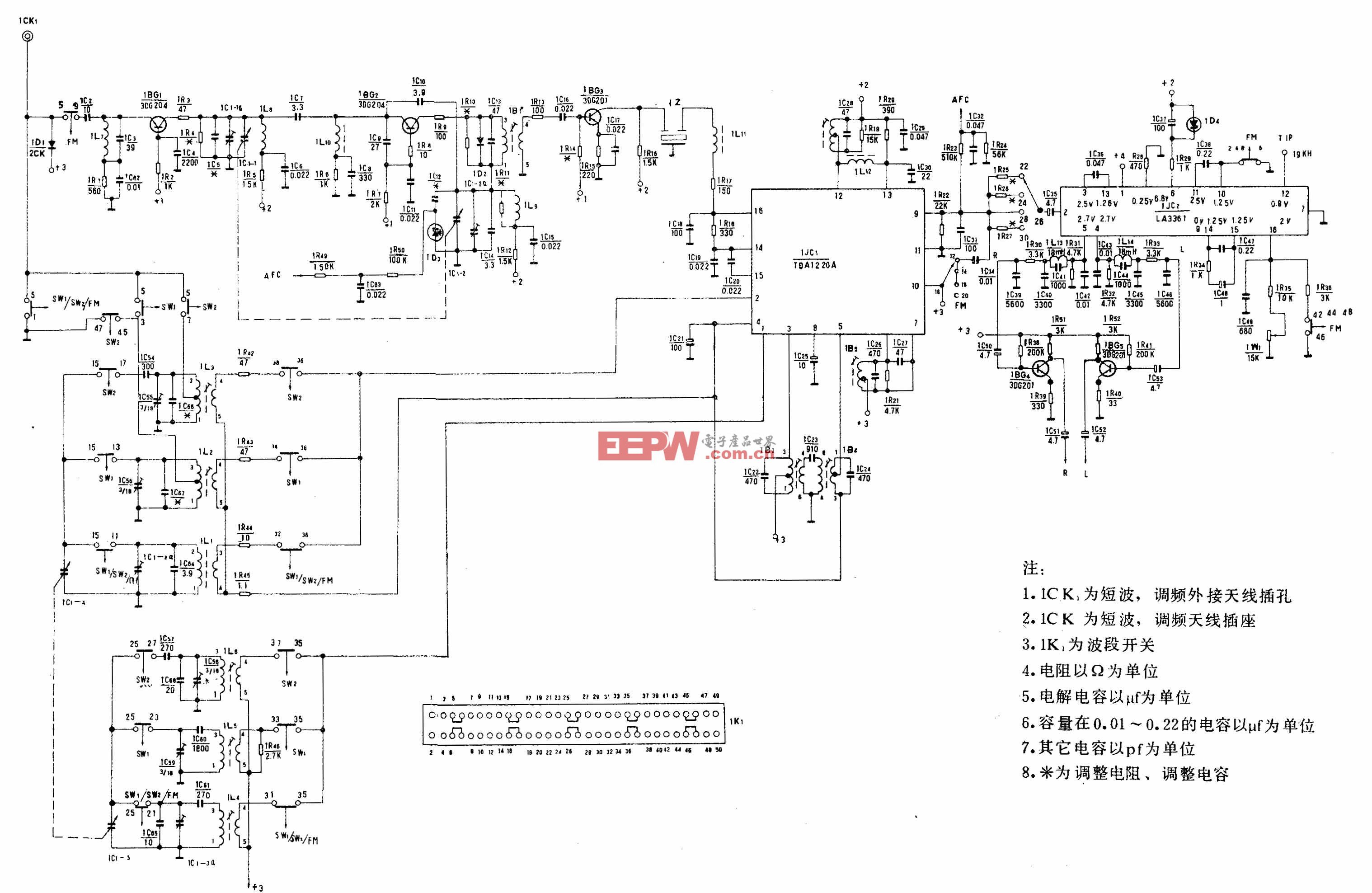

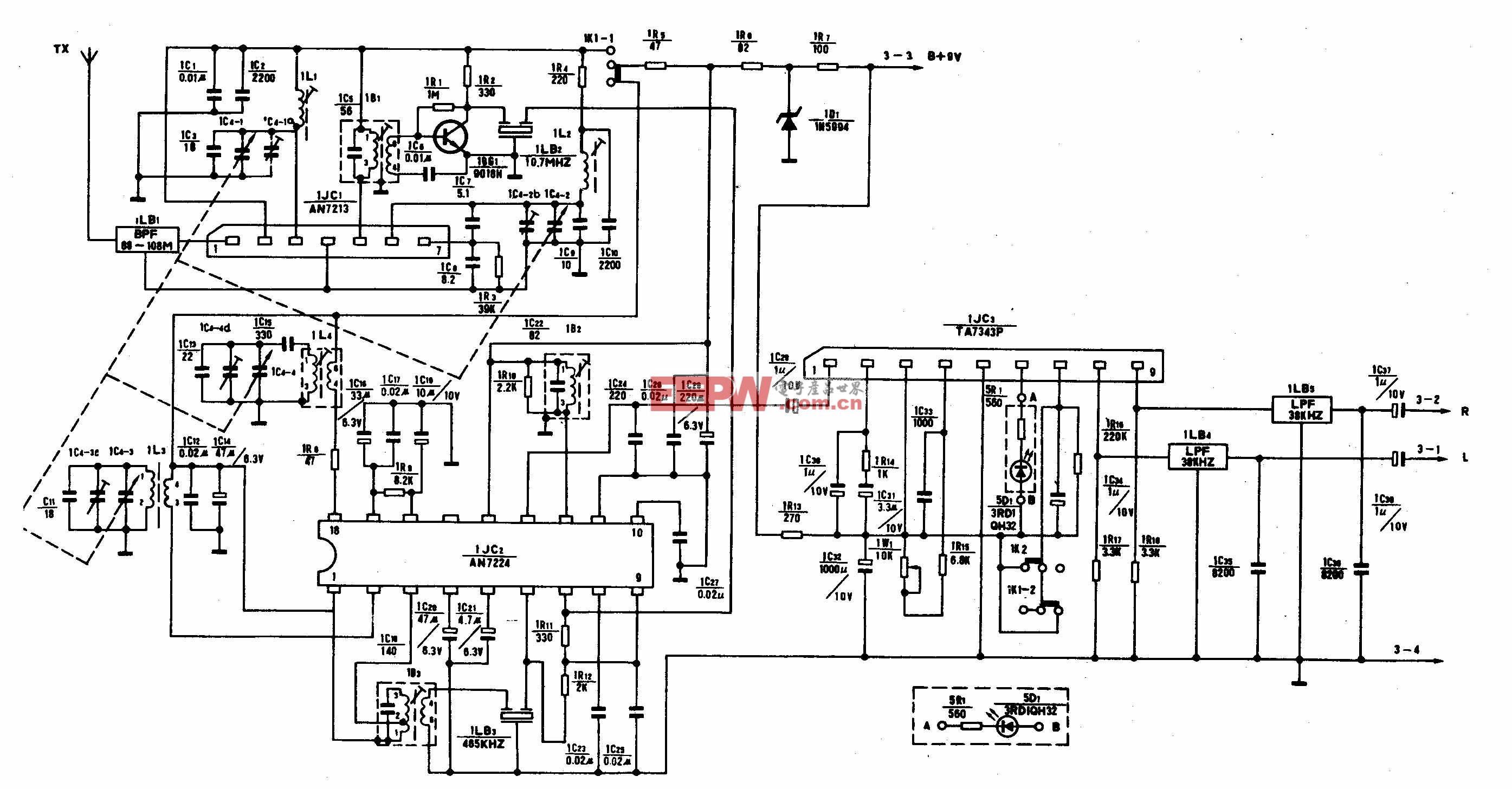

系統(tǒng)主要由正弦激勵信號的產(chǎn)生模塊和信號采集、處理和實時顯示模塊組成。其中前者采用基于“IP核+高速D/A”的思想產(chǎn)生掃頻信號,后者主要包括FPGA核心板、雙路高速A/D以及人機交互界面。在系統(tǒng)時鐘和觸發(fā)信號的驅動下,同時采集待測網(wǎng)絡的輸出信號以及系統(tǒng)的激勵信號,并進行相應的數(shù)據(jù)處理,實現(xiàn)對有源或無源四端網(wǎng)絡的幅頻特性測試。系統(tǒng)組成框圖如圖1所示。

系統(tǒng)設計中需要解決的核心問題:(1)51內(nèi)核的初始化配置問題。系統(tǒng)使用的51內(nèi)核,可以直接通過頂層文件的端口例化實現(xiàn)與FPGA內(nèi)部定義信號之間的連接,而51內(nèi)核使用的存儲器模塊則需要用戶進行配置。(2)數(shù)據(jù)流的速率匹配問題。經(jīng)A/D采集得到的數(shù)據(jù)率遠遠超出了51內(nèi)核的運算處理能力,因此系統(tǒng)中要進行數(shù)據(jù)緩存模塊的設計。(3)彩屏液晶的顯示控制。顯示部分是該儀器的關鍵模塊,系統(tǒng)采用TFT-LCD顯示技術,可以進行友好的人機界面設計,但是彩屏液晶的初始化時序極其復雜,在動態(tài)曲線和測量數(shù)據(jù)的實時顯示方面要進行優(yōu)化設計。這些問題在實際設計中均得到了合理解決。

1.2 測量原理

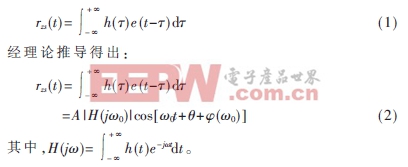

對于一個線性時不變(LTI)系統(tǒng),其沖激響應為h(t),在激勵為正弦信號e(t)=Acos(?棕0t+?茲)時,系統(tǒng)的零狀態(tài)響應為:

由此可以看出,系統(tǒng)輸出的穩(wěn)態(tài)響應也是一個正弦信號,其頻率和輸入信號的頻率相同,但幅度和相位發(fā)生了變化,其中幅度變?yōu)樵钚盘柗鹊膢H(j?棕0)|倍,|H(j?棕0)|稱為電路網(wǎng)絡幅頻特性。

系統(tǒng)工作時,將等幅的正弦掃頻信號作為輸入信號激勵被測網(wǎng)絡。掃頻信號的起始頻率、終止頻率、頻率步進值以及掃描時間均可以通過按鍵輸入的方式設置,也可以采用系統(tǒng)默認的設置方式(掃頻范圍1 kHz~1 MHz,頻率步進1 kHz,掃描時間1 s)。高速A/D采集網(wǎng)絡的輸出信號和原始激勵信號,并在FPGA內(nèi)通過峰值檢波程序得到網(wǎng)絡輸出信號的包絡數(shù)據(jù),同時與激勵信號的幅值比較計算不同頻點的增益數(shù)據(jù)。采用異步FIFO作為FPGA與51內(nèi)核之間傳輸數(shù)據(jù)的緩沖器,并將其配置為“乒乓”工作模式。當觸發(fā)信號到來時,將增益數(shù)據(jù)按照一定的格式和速率寫入異步FIFO。當FIFO中存儲一定數(shù)量的數(shù)據(jù)以后,在51內(nèi)核同步時鐘的控制下將數(shù)據(jù)讀出并送往LCD模塊,同時禁止數(shù)據(jù)繼續(xù)寫入FIFO,實現(xiàn)幅頻特性曲線的顯示。

2 系統(tǒng)硬件設計

系統(tǒng)硬件主要實現(xiàn)正弦掃頻信號的產(chǎn)生、網(wǎng)絡輸出信號的采集處理、數(shù)據(jù)的傳輸以及TFT液晶模塊接口電路等功能,硬件總體框圖如圖2所示。

2.1 FPGA核心板模塊

FPGA核心板模塊是系統(tǒng)的核心,根據(jù)需要設計出FPGA最小系統(tǒng)板以及相關的A/D、D/A電路。其中,F(xiàn)PGA最小系統(tǒng)板采用Xilinx公司Spartan3系列的XC3S400-PQ208型40萬門芯片,核心板采用5 V輸入,由3片AMS1117實現(xiàn)5 V到3.3 V、5 V到2.5 V和5 V到1.2 V的電平轉換。板上采用40 MHz有源晶振,滿足高速設計要求。A/D為ADI公司高速模/數(shù)轉換芯片AD9224,具有12位精度,且功耗低。D/A采用高性能高速率的AD9764AR芯片,該芯片具有14位分辨率和極佳的動態(tài)無雜波失真范圍。

2.2 掃頻信號源設計

掃頻信號源的性能指標直接影響儀器的測試精度,本文采用DDS技術產(chǎn)生掃頻信號。這里有兩條途徑可供選擇,一種是采用專用的DDS芯片,如AD9854等,利用FPGA發(fā)送頻率控制字產(chǎn)生掃頻信號;另一種是采用FPGA中集成的正弦查詢表IP核,這是一種利用“IP核+D/A”相結合來實現(xiàn)DDS技術的方法,在充分提高FPGA內(nèi)部資源利用率的前提下,又可以有效降低系統(tǒng)的硬件復雜度和成本,因此系統(tǒng)采用該方式。

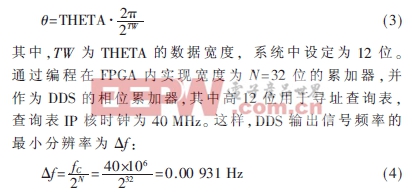

設計環(huán)境使用Xilinx公司的ISE7.1,通過Core Generator生成正弦查詢表IP Core,查詢表中的波形數(shù)據(jù)存儲在FPGA的塊存儲器(Block Memory)中。查詢表IP核的輸入相位控制字THETA與實際相位之間的關系為:

該頻率精度完全達到設計要求。

評論