基于DSP的高速數據采集系統硬件設計

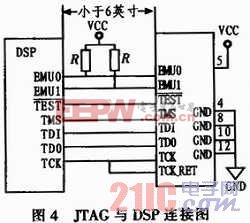

2.3 JTAG電路

JTAG是基于IEEE 1149.1標準的一種邊界掃描測試方式(Boundary-scan Test),結合仿真器和仿真軟件,可訪問DSP的所有資源,包括片內寄存器以及所有的存儲器,從而提供實時的硬件仿真與調試環境,便于開發人員進行系統調試。在大多數情況下,如果開發板和仿真器之間的連接電纜不超過6英寸,可以采用圖4的接法。但應該注意,DSP的EMU0和EMU1引腳都需要上拉電阻,推薦值為4.7 kΩ或者10 kΩ。如果DSP和仿真器之間的連接電纜超過6英寸,則需要另加緩沖驅動電路。

2.4 時鐘電路

TMS320VC5509的外部時鐘從CLKIN引腳輸入,在內部修改這個信號,來產生希望頻率的輸出時鐘,時鐘發生器將這個輸出時鐘(即CPU時鐘)送給CPU、外設和其他的內部模塊。也可以用可編程的時鐘分頻器對CPU時鐘分頻,在CLKOUT引腳輸出。時鐘發生器中還有一個時鐘模式寄存器(CLKMD),用來控制和監視時鐘發生器,它可以控制時鐘發生器進入兩種工作模式:

1)旁路模式,PLL被旁路掉,輸出時鐘的頻率就等于輸入時鐘的頻率除以1、2、4。

2)鎖定模式,輸入時鐘既可以乘以或除以一個系數來獲得期望的輸出頻率,并且輸出時鐘相位與輸入信號鎖定。

在鎖定模式下,輸出頻率由下面的公式計算:

輸出頻率=(PLL MULT/(PLL DIV+1))×輸入時鐘頻率

在此,可以選擇時鐘發生器工作在鎖定模式,即CLKMD的PLL ENABLE為1,外部振蕩晶體可以為10~20 MHz。根據外部振蕩晶體與DSP內部時鐘信號,可以計算出相應的PLLMULT與PLL DIV值,圖5為DSP的外部時鐘電路。

評論