基于QuickUSB的數據采集系統

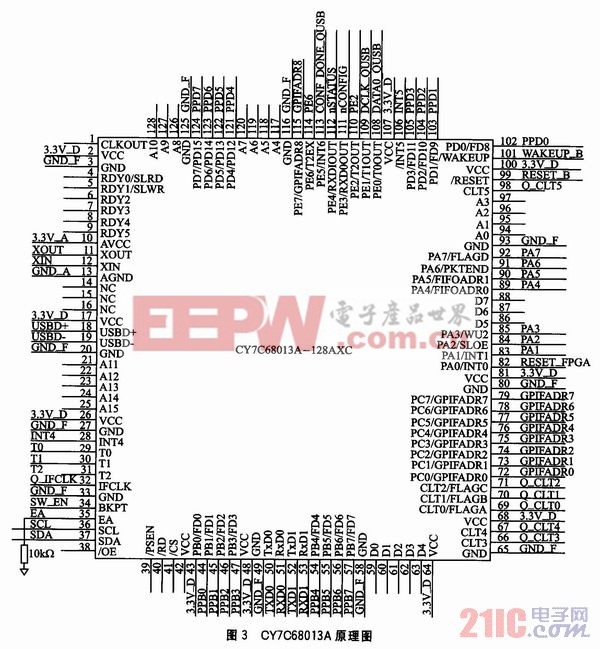

CY7C68013A原理圖設計如圖3所示。其中包括9根地址線(GPIF_ADR0~8),16根數據線(PPB0~7、PPD0~7),以及相應的控制線。本文引用地址:http://www.104case.com/article/194822.htm

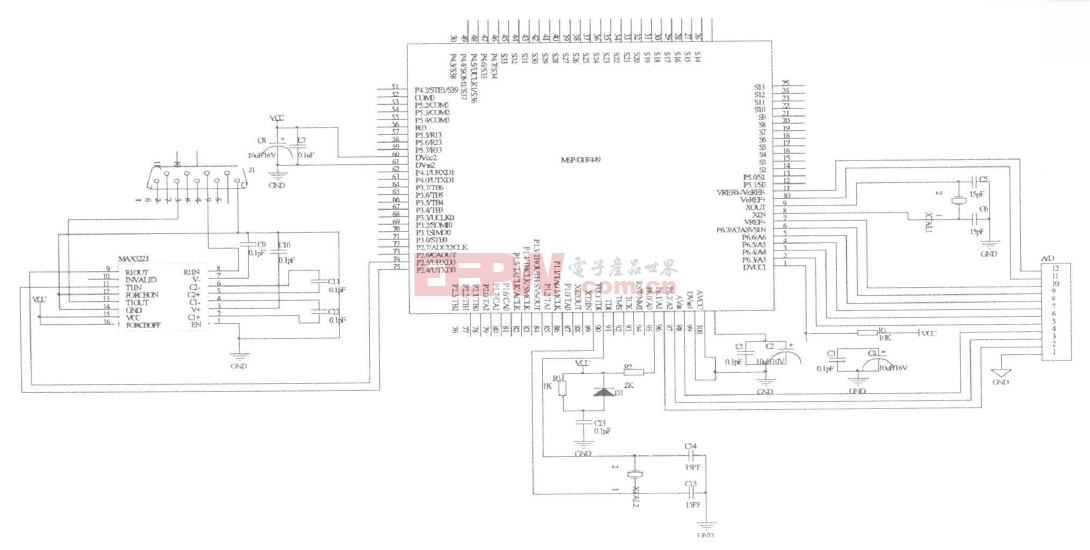

FPGA與CY7C68013A連接軟件界面如圖4所示。配合CY7C68013A設計編寫的相應讀寫控制時序,能夠與PC端進行通信,同時根據獲得的控制命令來對ADC進行操作,并將獲得的數據從FIFO中讀取出來,傳遞到PC端。

評論