瞬變光輻射采集系統設計

在電路中采用的方法是:A/D轉換器按照固定的轉換頻率進行模擬量到數字量的轉換,通過FPGA控制數據的變速率存儲。其具體的VHDL設計步驟如下:

(1)實現采樣時鐘的逐次分頻;

(2)調整逐次分頻的占空比,以防止數據存儲錯誤;

(3)設計使能信號,實現對每組只存儲32點。

由于系統對目標信號采集時間長度是固定的,故變頻存儲的變頻次數是有限的。初始存儲時間間隔△t=0.01 ms,其變頻次數不超過16次。故本方案中設計一個16位計數器counter16,對200 kHz采樣時鐘計數。計數器counter16的第0~15位的輸出,即可以實現對200 kHz采樣時鐘的逐次二分頻。但是由于從counter16(1)開始,每個低位輸出時對應著K個有效數據,但存儲的數據只會是最后一個有效數據,這樣可能會造成數據存儲出錯,故需要對counter16(1)~counter16(15)進行占空比調整。將占空比從1:1調整為1:(2K-1),其中K為整數(K=2~32 768)。調整占空比VHDL的思路為設計一個16位的counter16_v計數器,將counter16的相應位進行相與后賦給相應的counter16_v。

由于每組只存儲32個數據,因此對應每組還要設計相應的16 b使能信號dcnt。方法是對clk_200K計數,存儲開始后,開始64個clk_200K時鐘將第一組數據使能信號dcnt(o)置為高電平,然后保持低;接著對128個clk_200K時鐘將第二組數據使能dcnt(1)置為高電平,然后保持低。按照這種方法可將16個使能信號從dcnt(0)~dent(15)設置好。變頻存儲的使能頻率為ad_clk。本文引用地址:http://www.104case.com/article/194600.htm

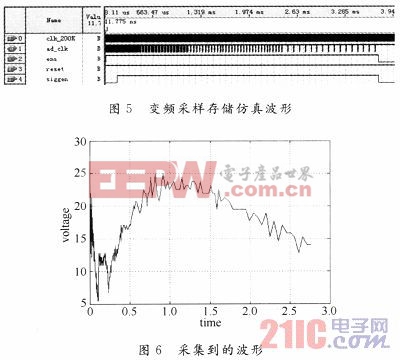

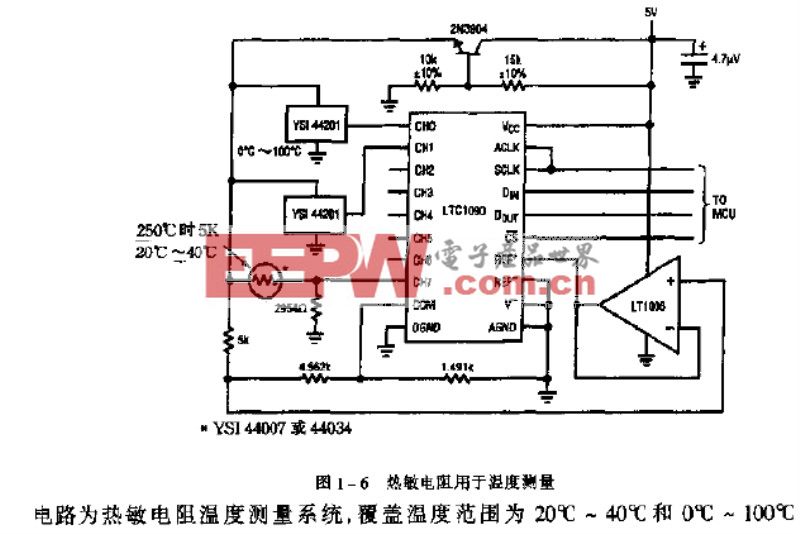

這里給出基于Altera公司的FPGA Flex10K系列的EPF10K20TC144-3。圖5為變頻存儲時,采樣頻率clk_200K與其他信號關系及其時序波形。系統先以默認的采樣頻率進行采樣,當識別檢測模塊判定信號發生時(siggen變為高電平),開始輸出經過變頻的采樣數據,每隔32點,存儲頻率下降50%,直到系統所要求的數據點數為止,采集到波形如圖6所示。當采樣的數據個數符合系統的要求后siggen信號變為低電平,ens屏蔽采樣的數據。等到FIFO清空后,ens重新變為高電平,恢復默認的采樣時鐘,重新開始采樣、識別和存儲工作。

4 結論

根據瞬態光輻射探測系統的整體要求,本文提出了基于目標信號特性基礎上的變頻采集方案,以FPGA為核心控制和處理單元,采用模塊化設計思想,編程實現對數據采樣和存儲的控制。按照工程要求,完成了編程、仿真和外圍硬件電路的搭建,實現了對瞬變光輻射信號的數據采集。該方案有效降低了數據采集系統對于存儲容量的要求,同時也減小了對數據處理量,對于其他數據存儲容量有要求的數據采樣系統具有很好的借鑒作用。

評論