CPLD用等占空比發生器連接兩個儀器

CPLD中可編程時鐘電路,為慢速儀器產生快速儀器等占空比的同步脈沖。

本文引用地址:http://www.104case.com/article/193511.htm同步兩個儀器信號時,保證接收器鎖存發送器的同步信號是重要的。例如,產生主脈沖信號時,脈沖發生器產生同步脈沖。Avtek的AV-1015B帶TTL的50Ω負載時,脈沖發生器的負載周期近似為50ns。本設計方案的目的是增加脈沖發生器高

電平寬度,滿足鎖相放大器的觸發要求。同步脈沖的頻率為鎖相放大器頻率范圍的10Hz到102 kHz。

由于同步脈沖與主脈沖同步,計算鎖相放大器同步輸入必須最小化任何延遲。由于使用者可從脈沖發生器改變脈沖序列的頻率,同步信號的頻率也可以改變。因此,無論使用者如何設置脈沖發生器的輸出,必須確保電路適合計算和產生同步信號。

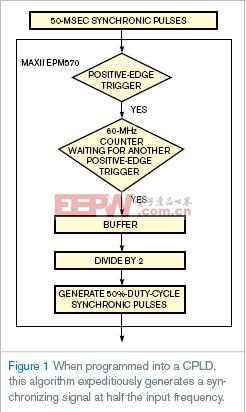

圖1所示為等占空比發生器的算法。CPLD首先等待正邊沿觸發,然后開始以60MHz的頻率計數,等待下一個正邊沿觸發。當下一個正邊沿到來時,同步信號的周期計數完成。計數值隨即被儲存到緩沖器,除以2得到等占空比發生器的值。

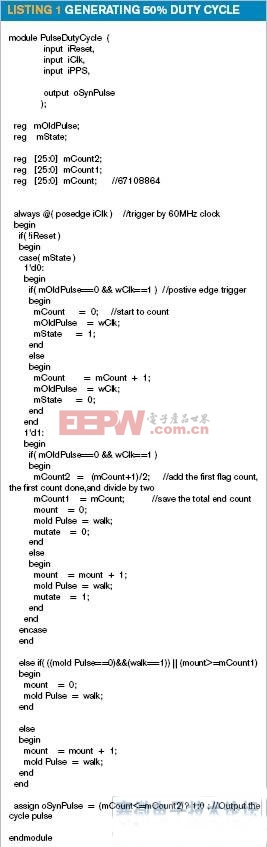

測試中,本設計方案等占空比發生器的頻率范圍覆蓋2Hz到450kHz。不僅可以用于脈沖發生器,還可以用于同步對其他系統觸發過窄的脈沖信號。等占空比發生器適合CPLD,例如帶60MHz系統時鐘和MM74HCT244緩沖器、輸出TTL信號的Altera EPM570。表1為CPLD程序。

英文原文:

CPLD connects two instruments with half-duty-cycle generator

A clocking circuit programmed into a CPLD generates a synchronizing pulse for a slower instrument at half the duty cycle of a faster instrument.

Yu-Chieh Chen and Tai-Shan Liao, National Applied Research Laboratories, Hsinchu, Taiwan; Edited by Charles H Small and Fran Granville -- EDN, 10/11/2007

When synchronizing two instruments’ signals, it is important to make sure that the receiver can latch the sender’s synchronous signal. For example, a pulse generator generates synchronizing pulses while generating the main pulse signal. For the Avtek AV-1015B, the pulse generator’s duty cycle is approximately 50 nsec at TTL with a 50Ω load. The goal of this Design Idea is to increase the pulse generator’s high-level width to meet the triggering spec of a lock-in amplifier. The synchronizing pulse’s frequency is 10 Hz to 102 kHz, which is the lock-in amplifier’s frequency range.

.

Because the synchronizing pulse synchronizes to the main pulse, you must minimize any delay in calculating the lock-in amplifier’s synchronizing input. And, because the user can change the frequency of the pulse train from the pulse generator, the synchronizing signal’s frequency also changes. Therefore, you must make sure that the circuit properly calculates and generates the synchronizing signal, no matter how the user sets the output of the pulse generator.

Figure 1 shows the half-duty-cycle generator’s algorithm. The CPLD first waits for the positive-edge trigger, then starts to count at a frequency of 60 MHz, and waits for the next positive-edge trigger. When the next positive edge comes, the synchronizing signal’s period counting is complete. The counting value then gets saved in a buffer and divided by 2 to yield the value for half-duty-cycle generation.

In tests, the half-duty-cycle ge

nerator in this Design Idea worked over a frequency range of 2 Hz to 450 kHz. You can use this design not only in a pulse generator, but also in any synchronizing signal in which the pulse is too narrow for other system triggering. The half-duty-cycle generator fits into a CPLD, such as an Altera EPM570 with a 60-MHz system clock and an MM74HCT244 buffer to output a TTL signal. Listing 1 contains the program for the CPLD.

評論