DDS技術在高頻石英晶體測試系統中的應用

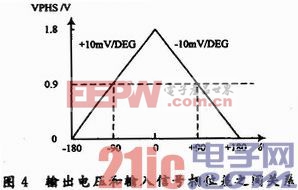

當被測晶體放入π網絡電路后,在不同的掃頻信號作用下,π網絡兩端輸入和輸出信號的相位差不同。π網絡兩端的輸入信號和輸出信號分別送入鑒相電路,在鑒相電路的輸出端得到與π網絡兩端輸入和輸出信號的相位差成正比的電壓信號。鑒相電路的輸出電壓信號和輸入信號相位差之間的關系如圖4所示。本文引用地址:http://www.104case.com/article/192856.htm

鑒相電路的輸出電壓信號經過信號調理電路轉變為適合于進行ADC采集的信號。信號通過STM32F103內置的12位ADC通道采集到處理器內部。測量過程時,DDS輸出信號的頻率由小變大,π網絡兩端輸入信號和輸出信號的相位差絕對值由大變小并逐漸接近于零,之后又由小變大。而ADC采集的結果則由小變大,到達最大值后,又由大變小。因此,這個最大值1.8 V處對應的DDS輸出信號頻率即為石英晶體的串聯諧振頻率。

2 DDS技術在測試系統中的應用

2.1 DDS技術

DDS有2個突出的特點,一方面,DDS工作在數字域,一旦更新頻率控制字,輸出的頻率就相應改變,其跳頻速率高;另一方面,由于頻率控制字的范圍寬,頻率分辨率高。與傳統的頻率合成器相比,DDS具有低成本、低功耗、高分辨率和頻率快速轉換等優點,廣泛應用于電子儀器儀表領域。

AD9912是ADI公司于2007年新推出的一款DDS芯片,內部時鐘速度可高達1 GSPS,并集成了14位數模轉換器,因此可以直接輸出400 MHz信號。AD9912采用48位頻率控制字,輸出頻率分辨率小于4μHz。AD9912兼容多種系統時鐘輸入方式,石英晶體、晶體振蕩器和外部時鐘都可以作為其系統時鐘輸入。由于具有片上系統時鐘鎖相環(PLL),允許系統時鐘輸入低至25 MHz。

2.2 信號源硬件設計

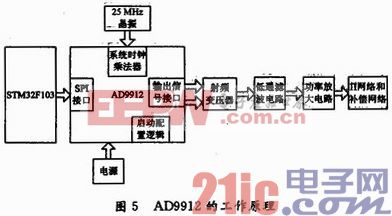

筆者選擇ADI公司的AD9912作為信號源的核心。STM32F103通過內置高速SPI總線控制AD9912輸出0~400 MHz的掃頻信號。AD9912的工作原理如圖5所示。

AD9912的外圍電路主要由5大模塊組成:電源、時鐘源、SPI通信接口、啟動配置邏輯、輸出信號處理電路。

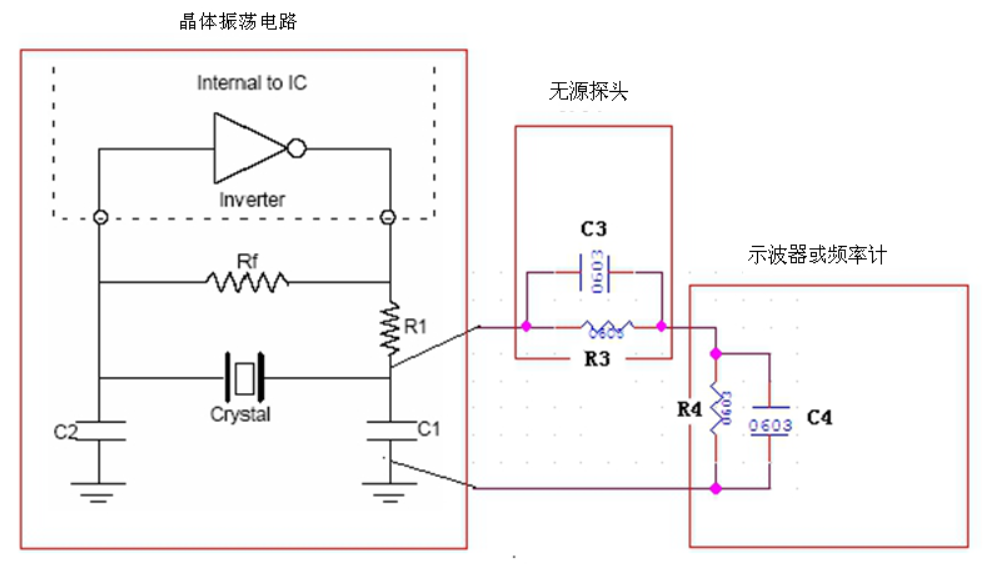

AD9912的電源分為模擬3.3 V、數字3.3 V、模擬1.8 V和數字1.8 V四大類。模擬3.3 V和數字3.3 V經過濾波器互相隔離。模擬1.8 V和數字1.8 V經過濾波器互相隔離。AD9912的參考時鐘選用25 MHz的高性能恒溫石英晶體,AD9912內部的PLL電路對該參考時鐘進行40倍倍頻得到1 000 MHz時鐘信號作為AD9912的系統時鐘。32管腳CLKMODESEL為時鐘模式選擇管腳,如果使用石英晶體作為系統時鐘輸入,該管腳應該接地,如果使用振蕩器或者外部時鐘源作為系統時鐘輸入,該管腳應被上拉至1.8 V。由于選用的是石英晶體,該管腳接地。

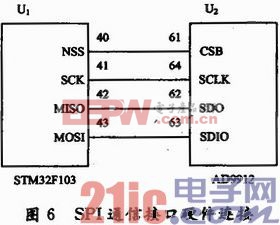

SPI通信接口硬件連接如圖6所示。

啟動配置邏輯包含S1,S2,S3,S4四個管腳。其中S4為邏輯0時,選擇時鐘模式:使用石英晶體作為系統時鐘輸入,并且由AD9912內部的PLL電路進行倍頻得到時鐘信號;S4為邏輯1時,選擇時鐘模式:由外部直接輸入時鐘信號。因此,把S4設置為邏輯0。S1、S2和S3的8種不同邏輯組合,用來選擇8組預置的16位頻率控制字。允許在未配置I/O寄存器的情況下,產生8種頻率不同的信號。由于本測試系統需要的是掃描信號,不需要某固定頻率的信號,因此,把S1,S2和S3設置為邏輯0,使DDS在啟動時不輸出信號。

評論