寬帶阻抗測量儀的設計――信號發(fā)生電路設計(一)

1.1方案選擇

本文引用地址:http://www.104case.com/article/192848.htm阻抗測量通常是向被測對象注入微小的正弦電流信號,同時通過測量電壓信號,以獲取相關的電阻抗信息。系統(tǒng)不僅要求正弦波信號波形失真小、幅值穩(wěn)定,而且必須具有頻率、幅值、相位可調(diào)節(jié)的功能。因此正弦波信號發(fā)生器的設計是阻抗測量系統(tǒng)的重要環(huán)節(jié)。

正弦波信號發(fā)生器主要有模擬式和數(shù)字式兩種類型。

模擬方法實現(xiàn)正弦波發(fā)生器優(yōu)點在于電路結(jié)構簡單、相對成本較低,輸出信號失真較小。但也存在明顯的不足,即電路的頻率、幅值調(diào)節(jié)困難。

早期的數(shù)字式信號發(fā)生器是采用向EPROM中寫入固定的數(shù)字化正弦波信號值,以一定頻率讀取正弦波表的內(nèi)存地址,將得到的數(shù)字信號進行數(shù)模轉(zhuǎn)換,再進一步通過低通濾波器將輸出的模擬階梯波去除高頻諧波,從而得到平滑正弦波電壓信號。此方法產(chǎn)生的信號穩(wěn)定可靠,頻率、幅值改變靈活,相移補償方便易行,但相對模擬方法電路復雜,造價較高。

直接數(shù)字頻率合成技術[21],即DDS(Direct Digital Frequency Synthesizer),是近年來迅速發(fā)展起來的第三代頻率合成技術。

DDS技術具有頻率轉(zhuǎn)換時間短、頻率穩(wěn)定度高、相位噪聲低、相位分辨率高等突出優(yōu)點。而且具有體積小,功耗低的特點,因此采用DDS技術對信號源電路進行設計是一種較為合適的方法。

1.1.1 DDS技術的優(yōu)點

1.輸出頻率相對帶寬較寬輸出頻率帶寬為50%f s(理論值)。但考慮到低通濾波器的特性和設計難度以及對輸出信號雜散的抑制,實際的輸出頻率帶寬仍能達到40%f s。

2.頻率轉(zhuǎn)換時間短DDS是一個開環(huán)系統(tǒng),無任何反饋環(huán)節(jié),這種結(jié)構使得DDS的頻率轉(zhuǎn)換時間極短。事實上,在DDS的頻率控制字改變之后,需經(jīng)過一個時鐘周期之后按照新的相位增量累加,才能實現(xiàn)頻率的轉(zhuǎn)換。因此,頻率轉(zhuǎn)換的時間等于頻率控制字的傳輸時間。時鐘頻率越高,轉(zhuǎn)換時間越短。DDS的頻率轉(zhuǎn)換時間可達納秒級,比使用其它的頻率合成方法都要短數(shù)個數(shù)量級。

3.頻率分辨率極高若時鐘f s的頻率不變,DDS的頻率分辨率就由相位累加器的位數(shù)N決定。只要增加相位累加器的位數(shù)N即可獲得任意小的頻率分辨率。目前,大多數(shù)DDS的分辨率在1Hz數(shù)量級,許多小于1MHz甚至更小。

4.相位變化連續(xù)改變DDS輸出頻率,實際上改變的每一個時鐘周期的相位增量,相位函數(shù)的曲線是連續(xù)的,只是在改變頻率的瞬間其頻率發(fā)生了突變,因而保持了信號相位的連續(xù)性。

5.輸出波形的靈活性只要在DDS內(nèi)部加上相應控制如調(diào)頻控制FM、調(diào)相控制PM和調(diào)幅控制AM,即可以方便靈活地實現(xiàn)調(diào)頻、調(diào)相和調(diào)幅功能,產(chǎn)生FSK、PSK、ASK和MSK等信號。另外,只要在DDS的波形存儲器存放不同波形數(shù)據(jù),就可以實現(xiàn)各種波形輸出。當DDS的波形存儲器分別存放正弦和余弦函數(shù)表時,既可得到正交的兩路輸出。

6.其他優(yōu)點由于DDS中幾乎所有部件都屬于數(shù)字電路,易于集成,功耗低、體積小、重量輕、可靠性高,且易于程控,使用相當靈活,因此性價比極高。

1.1.2 DDS技術原理及實現(xiàn)方法

直接數(shù)字頻率合成(Direct Digital Frequency Synthesis即DDFS。一般簡稱DDS)是一種新的頻率合成技術。同傳統(tǒng)的直接頻率合成(DS)、鎖相環(huán)間接頻率合成(PLL)方法相比,它具有很多優(yōu)點:頻率切換時間短、頻率分辨率高、相應變化連續(xù)、容易實現(xiàn)對輸出信號的多種調(diào)制等。

直接數(shù)字頻率合成是基于奈奎斯特抽樣定理和數(shù)字波形合成原理而發(fā)展起來的一種數(shù)字化的頻率合成技術。

DDS的基本原理是利用采樣定理,通過查表法產(chǎn)生波形。

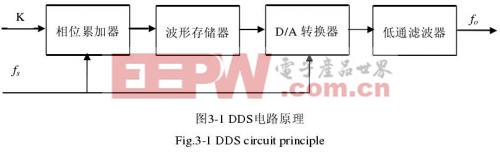

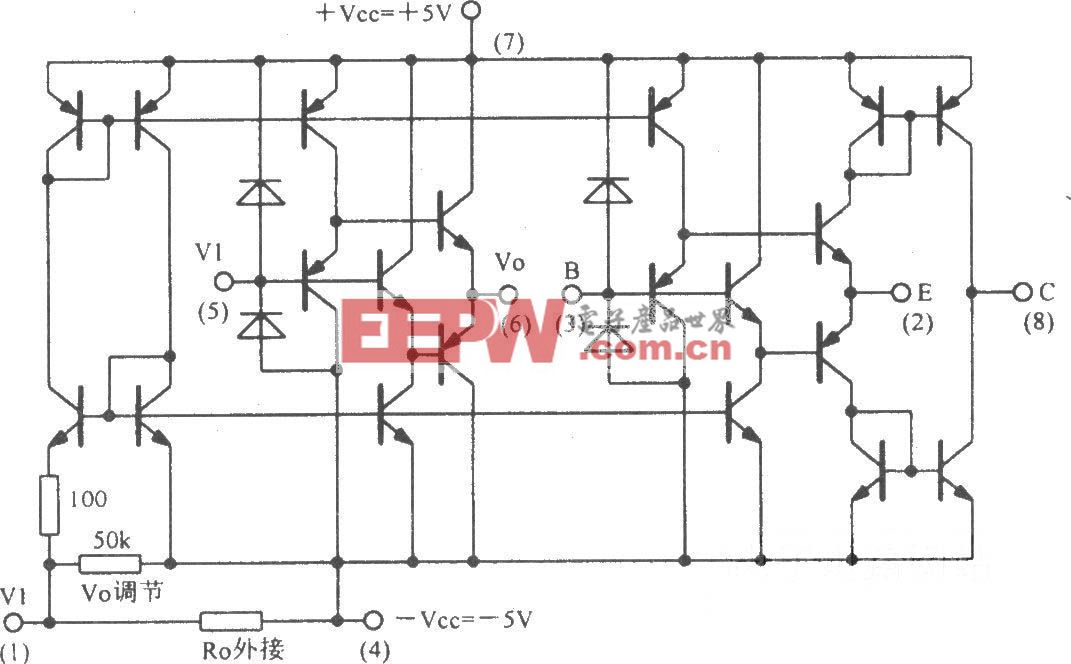

DDS的結(jié)構有很多種,其基本的電路原理如圖3-1所示。

相位累加器由N位加法器與N位累加寄存器級聯(lián)構成。每來一個時鐘脈沖f s,加法器將頻率控制字k與累加寄存器輸出的累加相位數(shù)據(jù)相加,把相加后的

結(jié)果送至累加寄存器的數(shù)據(jù)輸入端。累加寄存器將加法器在上一個時鐘脈沖作用后所產(chǎn)生的新相位數(shù)據(jù)反饋到加法器的輸入端,以使加法器在下一個時鐘脈沖的作用下繼續(xù)與頻率控制字相加。這樣,相位累加器在時鐘作用下,不斷對頻率控制字進行線性相位累加。

由此可以看出,相位累加器在每一個時鐘脈沖輸入時,把頻率控制字累加一次,相位累加器輸出的數(shù)據(jù)就是合成信號的相位,相位累加器的溢出頻率就是DDS輸出的信號頻率。用相位累加器輸出的數(shù)據(jù)作為波形存儲器(ROM)

的相位取樣地址,這樣就可把存儲在波形存儲器內(nèi)的波形抽樣值(二進制編碼)經(jīng)查找表查出,完成相位到幅值轉(zhuǎn)換。

波形存儲器的輸出送到D/A轉(zhuǎn)換器,D/A轉(zhuǎn)換器將數(shù)字量形式的波形幅值轉(zhuǎn)換成所要求合成頻率的模擬量形式信號。

低通濾波器用于濾除不需要的取樣分量[22],以便輸出頻譜純凈的正弦波信號。

DDS在相對帶寬、頻率轉(zhuǎn)換時間、高分辨力、相位連續(xù)性、正交輸出以及集成化等一系列性能指標方面遠遠超過了傳統(tǒng)頻率合成技術所能達到的水平,為系統(tǒng)提供了優(yōu)于模擬信號源的性能。

DDS的實現(xiàn)方法有以下幾種方案:1.采用高性能DDS單片電路的設計方案;2.采用低頻正弦波DDS單片電路的設計方案;3.自行設計的基于FPGA芯片的設計方案;在對DDS性能要求不苛刻、控制要求靈活的應用場合,優(yōu)先選用基于FPGA設計的DDS電路;在需要的頻率點很多,特定頻率時諧波失真要求較小的場合,優(yōu)先選用低頻正弦波DDS單片電路;而在對輸出信號性能要求高的場合,則優(yōu)先采用采用高性能DDS單片電路,這樣可以減小設計和調(diào)試難度。

而基于本系統(tǒng)的寬頻帶、分辨率高的設計要求,采用高性能DDS單片電路的設計方案。

1.1.3 DDS芯片的選擇

目前,市場上性能優(yōu)良的DDS產(chǎn)品己不斷推出,Qualcomm公司的Q2220,Q2234,Q2368等產(chǎn)品。

Q2334在30MHz的時鐘上可以高達0.007Hz的頻率分辨率提供10MHz以上的信號,而幅度量化噪聲低于信號幅值72dB,但由于價格昂貴,因此主要用于擴頻通信、電子戰(zhàn)等尖端領域;Sciteq公司相繼推出了系列化的DDS產(chǎn)品,其中ADS-431,時鐘頻率1.6GHz,可正交輸出,分辨率1Hz雜散-45dBc,捷變時間30ns;美國Stanford公司也相繼推出了系列化的DDS產(chǎn)品,如STEL-2171,GaAs電路,時鐘頻率1GHz,分辨率0.3Hz,雜散-55dBc,捷變時間25ns,這兩種都需要直接輸入比較高的系統(tǒng)時鐘頻率,而且采用GaAs電路,價格昂貴。

評論