超聲波隨鉆井徑檢測儀的數據采集與傳輸

2.1 AD控制模塊的設計與實現

AD控制模塊要實現的功能是提供AD轉換的片選信號和AD轉換時鐘,以及FIFO的寫時鐘、FIFO要存儲的16位并行數據,接收AD轉換的串行數據并實現串轉并,同時提供換能器的激勵信號。本設計中,AD轉換芯片采用的是ADI公司的12位AD7352,該芯片具有耐高溫、功耗低等優點。片選信號CS的周期決定了AD采樣的速率,FPGA為AD提供的轉換時鐘SCLK的頻率大小決定了AD的轉換時間,正常工作時,完成一個數據的轉換至少需要14個時鐘下降沿。在本設計中,綜合考慮各方面的因素,AD采樣頻率設計為2.5 MHz,完成一個模擬量的轉換采用18個轉換時鐘,這樣,AD的轉換時鐘SCLK的頻率為45 MHz,該時鐘由FPGA中鎖相環對50 MHz的系統時鐘分頻得到。片選信號CS高低電平的控制采用計數器對與轉換時鐘相同的時鐘計數來實現,每當該時鐘的上升沿到來時,計數器加1,計數器加到17后,又從零開始循環計數,當計數器的值小于14時,將片選信號CS置低,否則置高。片選信號與轉換時鐘的時序如圖3所示。本文引用地址:http://www.104case.com/article/192799.htm

在本部分設計中,考慮到實際應用中需要對四個換能器接收的數據進行采集,為了區別各個換能器的數據,設計時在串轉并的過程中人為添加了四位數據作為標志位。為了使AD的采樣率、FPGA中串轉并的速率以及FIFO的寫速率保持一致,FIFO的寫時鐘采用一個計數器對AD的轉換時鐘計數獲得。每當轉換時鐘SCLK的下降沿到來時計數器加1,計數器從零到13循環計數,計數器每循環一個周期就提供一個寫時鐘上升沿(寫時鐘上升沿有效),使FIFO完成一次寫操作。在AD正常工作時,第一個時鐘下降沿會輸出兩個前導零,然后從第二個時鐘下降沿開始依次從高位到低位輸出12位有效的數據,并在第13個下降沿完成最后一位數據的輸出,最后在之后的上升沿返回跟蹤模式。因此,在串轉并時,要從第二個時鐘下降沿開始。

2.2 FIFO的設計與實現

FIFO的主要功能是實現不同時鐘域之間的數據傳輸。FIFO分為同步FIFO和異步FIFO,本設計中采用的是異步FIFO,涉及到的主要參數包括FIFO的深度,FIFO的讀、寫時鐘,FIFO存儲的數據的寬度和讀、寫指針等。考慮到AD采樣速率為2.5 MHz,每次開始轉換后持續的時間大約為600 μs,因此,FIFO需要緩存的數據大約為1 500個,Actel公司的APA075中有12個256X9的RAM空間,最多能緩存1 536個16位的數據。

為了保險起見,FIFO的深度設計成1 536,根據實際應用的需求,FIFO的寬度設計成16位,寫時鐘頻率和AD采樣頻率保持一致,讀時鐘頻率和串口傳輸速率保持一致。同時,為了防止數據溢出或讀取無效的數據,FIFO的設計采用了空滿標志位。當FIFO寫滿時,滿標志位置1,禁止繼續向FIFO中寫入數據:當FIFO為空時,禁止從FIFO中繼續讀取數據。空滿標志的準確判斷是FIFO設計的一大難點,本設計中采用了列舉的算法實現空滿標志的判斷。FIFO寫滿有以下兩種情況:第一,寫指針加1等于讀指針,并且寫使能有效,再繼續寫操作時,FIFO就為滿,滿標志位置1;第二,寫指針加1等于FIFO的深度并且讀指針為零,再繼續寫操作時,FIFO就為滿,滿標志位置1。與滿標志情況類似,FIFO讀空也有以下兩種情況:第一,讀指針加1等于寫指針,再繼續讀操作時,FIFO就為空,空標志位置1;第二,讀指針加1等于FIFO的深度并且寫指針為零,再繼續讀操作時,FIFO就為空,這時,空標志位置1。

2. 3 串口發送的設計與實現

串口發送模塊負責把處理后的數據從FIFO中讀出,將其按通信協議傳送給MAX232完成電平轉換后送給PC機。發送數據采用的波特率是9 600,數據幀格式如圖4所示。

本設計的數據幀格式為1位起始位,8位數據位,1位停止位,沒有奇偶校驗位,本設計采用連續兩次發送來解決發送16位數據的問題。為了保持讀FIFO的速率與發送數據的速率一致,FIFO的讀時鐘根據串口發送一個完整數據的速度來確定。

3 測試結果

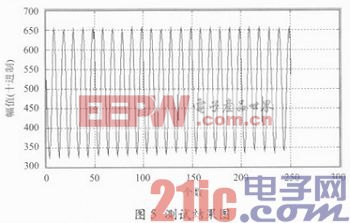

在實驗室自制的最小系統板上,模擬換能器給AD提供一個250 kHz的正弦信號,在上位機串口調試小助手上接收到的數據運用Matlab畫出的圖形如圖5所示。圖5中,縱坐標是幅值,橫坐標是所取點的個數。

4 結語

可以看出,本設計中每個周期的正弦波包含有10個點。由于我們輸入的是250 kHz的正弦波,AD采樣頻率是2.5 MHz,通過理論計算,每個周期應該包含的點數為2.5 MHz/250 kHz=10,可見設計與實際測試的結果相符。另外,從測試結果圖中還可以看出,其幅值與所給的幅值也相符,測試結果也表明了該設計的合理性。

fpga相關文章:fpga是什么

評論