模擬乘法器ADL5391的原理與應用

3.1 寬帶乘法器

3.1.1 寬帶乘法器電路設計

對于ADL5391,當輸入X、Y、Z與輸出W為差分驅動時,其性能最佳。另外,ADL5391也可以進行單端驅動。單端至差分轉換(或者差分至單端轉換)可以通過傳輸線變壓器來實現。在沒有交流耦合電容的情況下,如果ADL5391使用單端驅動,則需要將2.5 V作為參考電壓。高于2.5 V的電壓是正電壓,低于2.5 V的電壓是負電壓。需要注意ADL5391不能負載太重,其最大參考電流是50 mA。本文引用地址:http://www.104case.com/article/192751.htm

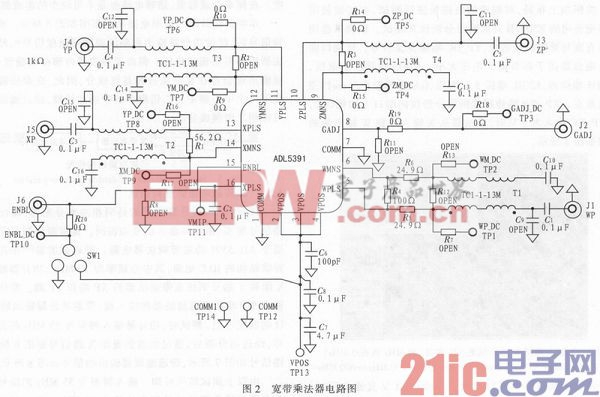

寬帶乘法器電路如圖2所示,為了實現最佳性能,通過傳輸線變壓器以差分形式驅動輸入端口X、Y、Z和輸出端口W,其中傳輸線變壓器選用的是Mini-Circuits TC1-1-13M,該傳輸線變壓器插入損耗小,工作頻帶寬,最高可工作在3 GHz。電阻R1、R2、R3、R12均為匹配電阻,因為X、Y、Z輸入端的輸入阻抗是相同的,所以為實現阻抗匹配,對于相同的頻率,R1、R2、R3應該是相同的。

ADL5391電源電壓允許范圍為4.5~5.5 V,一般采用5 V,因此,VPOS端接5 V電壓,COMM1和COMM端均為接地端。圖中,J1、J3、J4、J5采用的是單端、高頻操作,XP、YP是乘法射頻輸入端,ZP是加法射頻輸入端,WP是射頻輸出端口,TP4、TP5、TP6、TP7、TP8、TP9為直流輸入端,電壓范圍為0~2.5 V,TP1、TP2為直流輸出端。ENBL為高使能端,接5 V電壓時,ADL5391芯片開始正常工作。GADJ端電壓驅動范圍是0~2 V,用于調節乘法器增益α,GADJ懸空時,α=1或0 dB。若VGADJ=0 V,則增益大約降低4 dB;若VGADJ=2 V,則增益大約提高6dB。VMID端為參考輸出端,當輸出電壓為Vpos/2時,則表明ADL5391芯片正常工作。

3.1.2 寬帶乘法器電路的性能測試

基于以上設計電路,利用Altium Designer Summer 09進行PCB布局設計。對于射頻電路PCB設計而言,元器件的布局不僅直接影響到電路本身的干擾及抗干擾能力,這也關系到所設計電路的性能。因此,在進行射頻電路PCB設計時除了要考慮普通PCB設計時的布局外,主要還需考慮如何減小射頻電路中各部分之間相互干擾,如何減小電路本身對其它電路的干擾以及電路本身的抗干擾能力。

在布局時,調整器件盡可能使RF路徑最短,RF路徑上過孔數量盡可能少,這樣可以減小路徑電感。電感不要并行靠在一起,這將形成空芯變壓器并相互感應產生干擾信號,應將它們垂直排列將互感減到最小。避免長距離走線,盡可能拉開線與線之間的距離。由于該芯片正常使用時,芯片溫度約為60℃,所以在該電路板上使用了大面積接地敷銅,以增強電路的抗干擾性及散熱性。據此,該寬帶乘法器電路的PCB設計如圖3所示。

評論