多端口寄存器堆的低功耗設計方法

2.2 減小負載電容

由式(2)可知,在轉換頻率和電源電壓固定的條件下,位線功耗的優化的另一種方法是降低位線電容,通過對存儲體陣列進行分割,減少位線上的存儲單元數目,來實現負載電容的減小。而且對于大容量的寄存器堆,字線上連接的存儲單元的數目也很大,它的功耗將隨陣列列數的增加而成線性增加,而位線的延遲將隨陣列行數的增加成平方關系增大。采用字線分割和位線分割技術可以將存儲陣列進行分塊來減小字線和位線上的負載電容及連線延遲。但是分的塊數過多又會帶來過多的輔助電路的開銷,文獻列出了各種陣列分割方法的功耗優化算法,通過綜合由分塊結構帶來的功耗節約和功耗開銷,最終確定寄存器堆的分塊結構,才能達到減小功耗的目的。

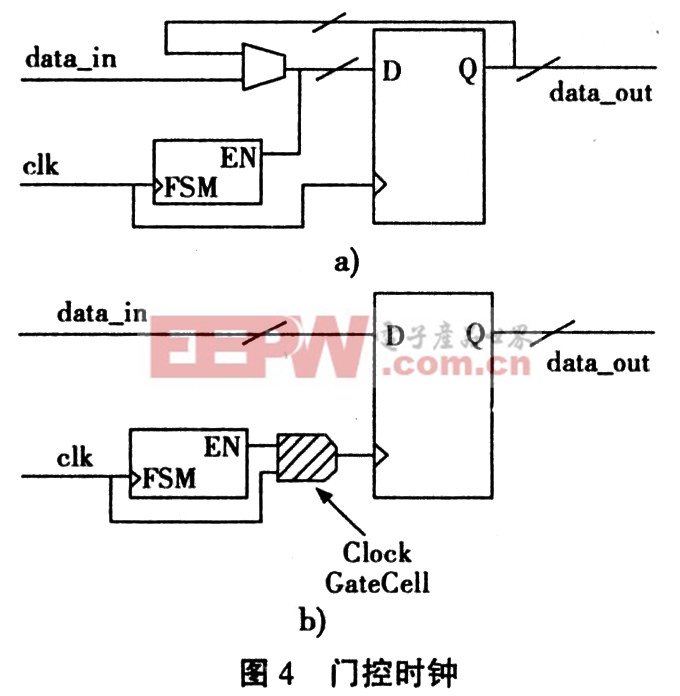

2.3 采用門控時鐘

由式(1)和式(2)可知,大部分的功耗都是由邏輯轉換期間電路中電容的充放電引起的動態功耗,因此動態的關閉處于空閑狀態邏輯的時鐘,減少電路中冗余的狀態翻轉,降低開關的活動頻率f,使更多的邏輯電路單元處于未激活的狀態來降低功耗。采用門控時鐘,通過在空閑狀態隔離開時序元件和時鐘網絡來減少功耗,是一種降低動態功耗的有效技術。

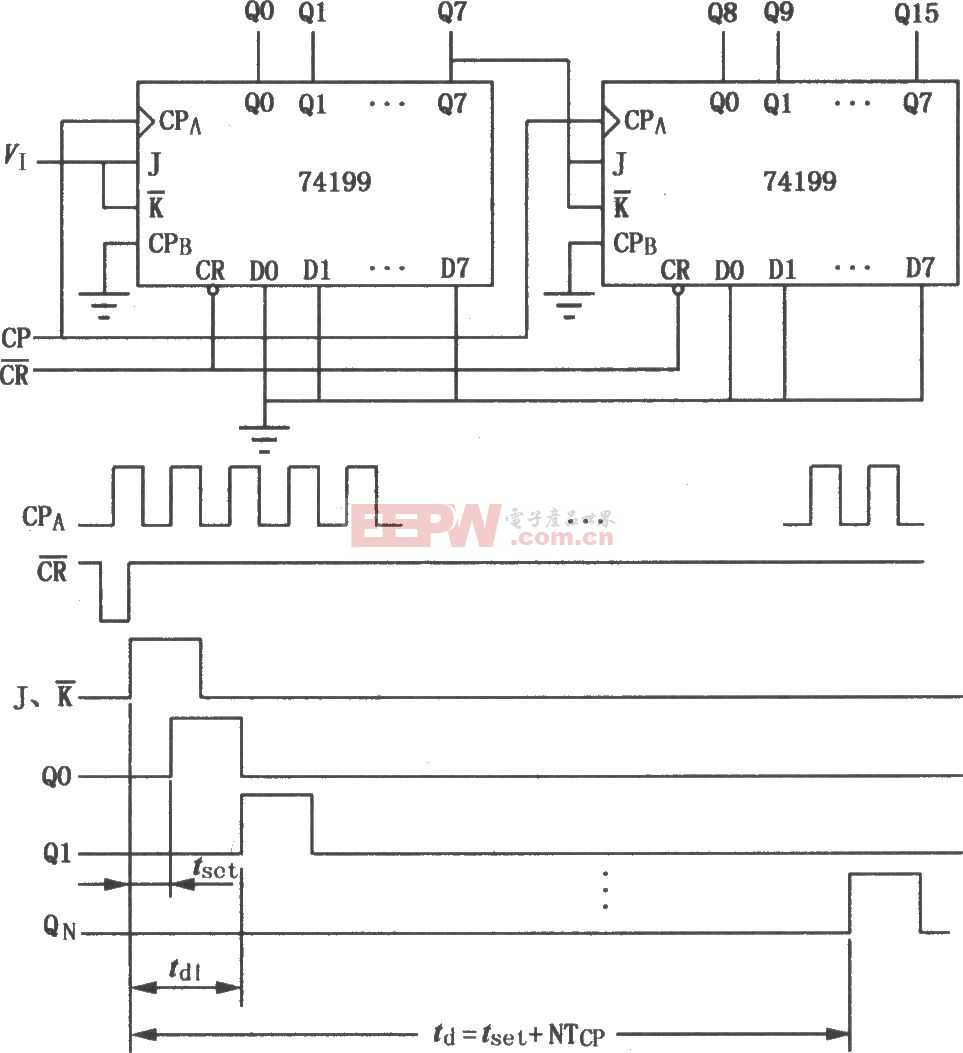

門控時鐘是通過一個控制信號來使能寄存器的時鐘端,當使能信號有效時時鐘翻轉,否則時鐘保持穩定,讓部分電路處于空閑狀態,達到節省功耗的目的。圖4給出了門控時鐘的示意圖,圖(a)是傳統的寄存器設計,無論數據端輸入數據更新與否,寄存器的時鐘端始終處于翻轉狀態,如果寄存器需要保持原來的狀態,還需要將寄存器的輸出數據反饋回輸入端與輸入信號進行選操作,由控制邏輯產生的選擇信號En決定寄存器輸出數據。圖(b)是采用門控時鐘后的電路,En作為使能信號,只有當它有效時,寄存器實際的時鐘輸入端才會產生脈沖,將輸入的數據更新到寄存器。門控時鐘可以切斷空閑時鐘,減小時鐘線的負載電容,降低動態功耗。同時在控制電路的設計中,可以采用門控時鐘對分塊的存儲陣列進行控制。通過門控時鐘控制信號使能,某一時刻僅有要使用的塊被選中激活,其他塊處于待命狀態,這樣就大大降低了整個寄存器堆的功耗了。

2.4 靈敏放大器

寄存器堆中的靈敏放大器是存儲單元讀操作中的關鍵部分,高速的靈敏放大電路可以降低位線上的電壓擺幅,減小敏感放大器功耗,降低讀操作的時間。

讀操作位線功耗可由下式估算:

![]()

其中,Lcell是存儲單元的電流,Tw1是字線上脈沖的寬度。

要降低讀操作的功耗,由上式可知,只要降低Lcell和Tw1即可。而Icell必須要大于靈敏放大器工作的輸入電流。因此,盡量采用低工作電流的靈敏放大器成為減小讀操作位線功耗的重要途徑。

通常的電壓型靈敏運放為了避免電壓的小幅擺動,往往采用層次結構,但這樣帶來的不利是延時和功耗的增加,電路變得復雜。電流型的靈敏運放電路能夠快速檢測到位線上電流的小幅擺動,而且可以降低讀操作的功耗,成為高速SRAM設計的首選。當它工作時,位線電平幾乎保持不變,因而基本上消除了位線電容充放電引起的功耗,但是代之以短路電流功耗,如果不對接地電流進行限制,就會大大抵消抑制位線電容充放電帶來的功耗節省,甚至可能增加功耗。差分電流型的靈敏運放電路能提高寄存器堆的讀取速度,并且有效地降低靈敏放大器功耗。因此,針對不同規模的寄存器堆,要選擇合適類型的靈敏放大器,才能達到高速低功耗的要求。

3 總結

多端口寄存器堆的低功耗不能僅僅針對某個單元或某個部分進行,而應該結合它的基本組成單元和它的電路結構,分析其功耗組成,從中找到節約功耗的有效方法。本文總結了幾種降低多端口寄存器堆功耗的方案,對各個組成電路結構,有針對性地進行功耗優化,包括降低字位線電壓擺幅,減小負載電容,采用門控時鐘,以及選用合適的靈敏放大器等方法,從而達到降低寄存器堆總功耗的目的。

評論