智能卡抗DPA攻擊的設計與實現

對于智能卡的DPA攻擊,主要是利用在卡上嵌入式微處理器運作時,某個特定指令的執行或數據存取所消耗功率,在供應電壓源上所表現特定的電流頻譜提供的有用信息。故可以通過外加額外的電路造成額外的電流消耗,從而改變電流頻譜以達到抗DPA攻擊。同時額外的電流消耗電路必須通過采用隨機數隨機的方式,產生隨機數消耗電流,以達到芯片消耗電力無法預測性,使其不能被分析與統計。

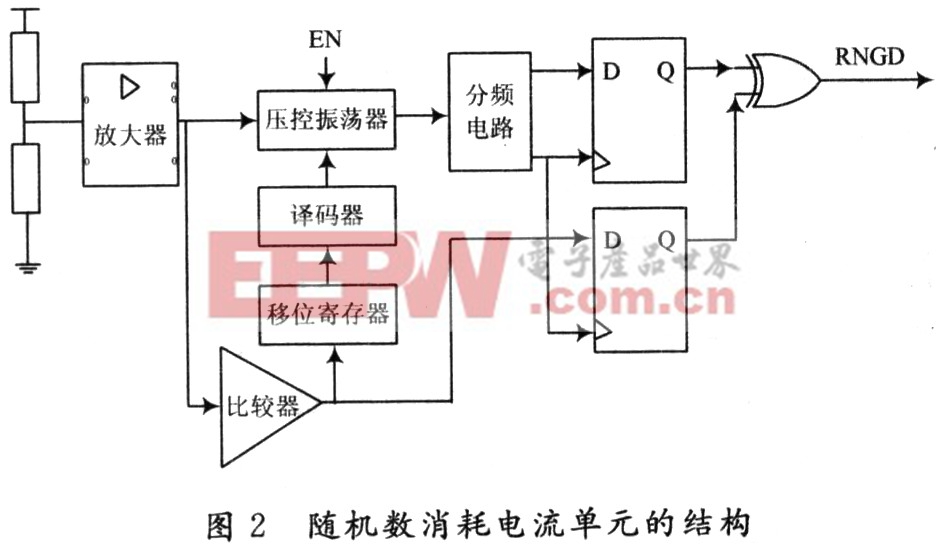

為此,可以在隨機數產生電路中設計如圖2所示的隨機數消耗電路,電路由比較器、移位寄存器、譯碼器組成;當電阻噪聲產生的噪聲電壓經過放大器、比較器后,產生“1”或“0”數字信號,存入移位寄存器,這樣寄存器內的值已經類似混沌式RNG所產生的隨機數,此隨機數經譯碼器編碼后,控制三態充放電緩沖器的充放電個數,最終達到以隨機數控制電流消耗的目的。本文引用地址:http://www.104case.com/article/188877.htm

3.2 組合邏輯防DPA攻擊設計

防DPA攻擊的主要目的是使電路特性在運算時保持相同,而保持電特性相同很重要的一點是使翻轉的晶體管數量在任何運算步驟中都是一個常數。為實現這個目的可在電路運算步驟之間增加一個中間步驟,這樣能防止有用信息從功耗分析中泄漏出去。最簡單的中間步驟設置是在輸入參數和電路運算完成之后設置系統中間值。

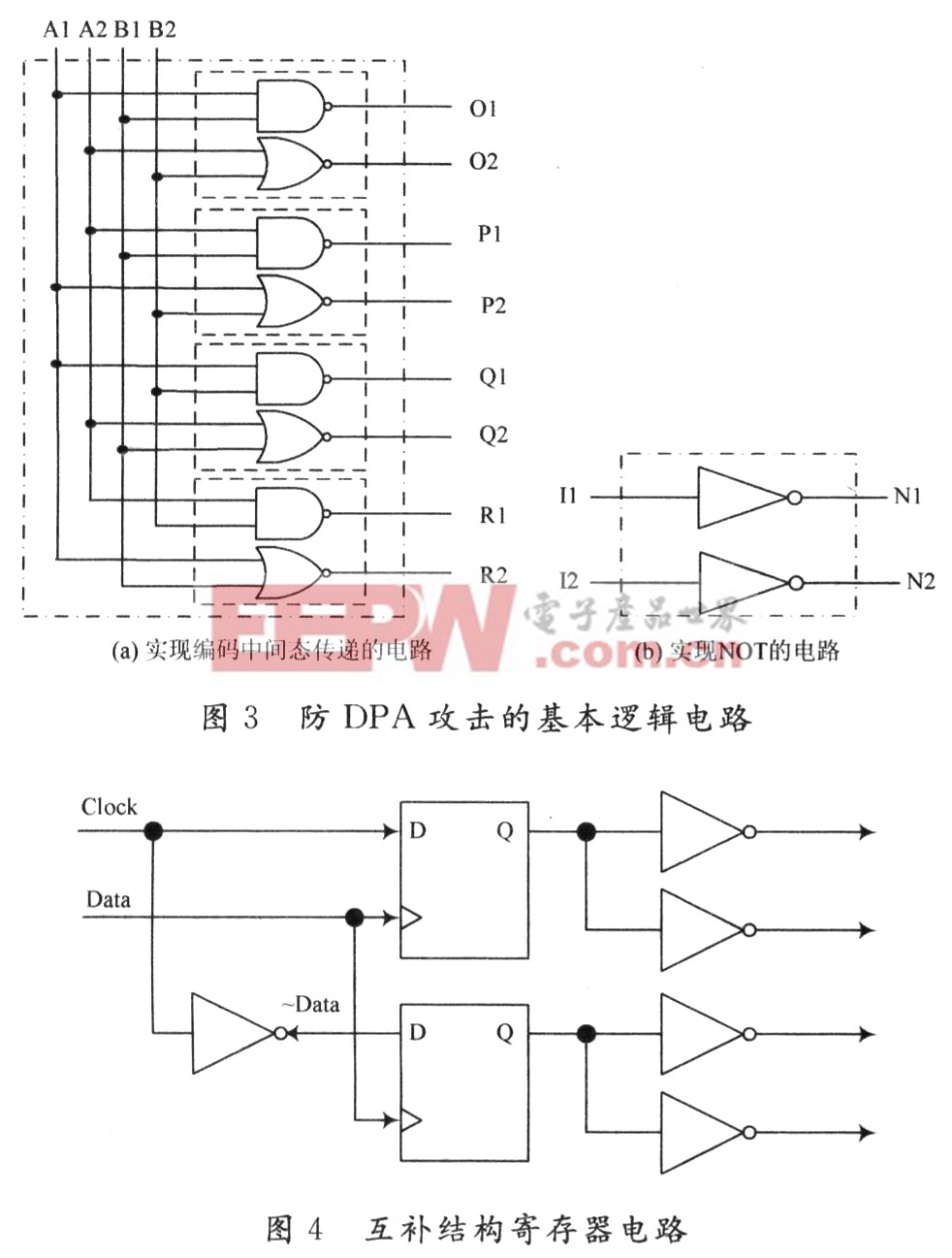

為此,參考異步邏輯電路的雙軌編碼方式中對信息的每一位用兩根信號線進行編碼的方式。采用兩位信號線的組合值“01”和“10”來表示數字邏輯的“真”和“假”,而組合值“00”和“01”則為中間值。這樣的編碼方式下,設計的基本邏輯單元電路如圖3所示。

如圖3(a)電路對于輸入A(A1A2)和B(B1B2),輸出只有O1O2和R1R2有效,當輸入A1A2B1B2為0000或1111時,輸出O1O2和R1R2的值是11或00,這樣實現了編碼中間態的傳遞。而當輸入A1A2B1B2為有效數據0101,0110,1001和1010時,輸出O1O2和R1的值就得到相關的NAND,AND,NOR和OR四個邏輯功能;其中,輸出O1O2→NAND,O2O1→AND,R1R2→NoR,R2R1→OR。至于NOT的實現如圖3(b)的電路所示。所以,上述基本的邏輯電路足以實現復雜的數字組合邏輯運算功能。

3.3 時序邏輯防DPA攻擊設計

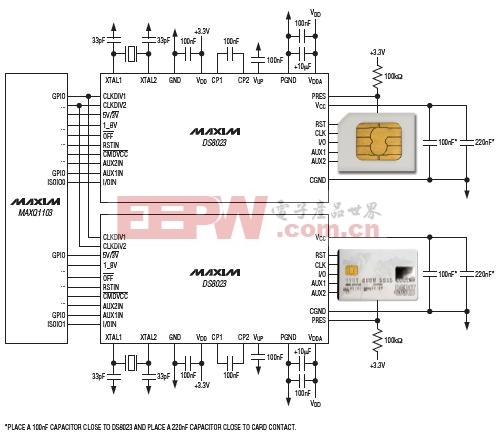

針對差分功耗分析,除了利用增加電路噪聲以降低差分功耗分析的信噪比的防御方案外。通過減小差分功率信號的值,同樣可以降低差分功耗分析的信噪比;若電路不同狀態下的功率差異趨于零,則差分功耗分析將失效。于是基于上述思路,在時序邏輯電路設計上可采用如圖4所示的互補結構寄存器電路。

設寄存器初始狀態相同,輸出負載相同,時鐘沿賦值,如圖4不論輸入為O或1,兩個互補寄存器必是一個翻轉,另一個不翻轉,因此總的功耗在兩種情況下沒有差別。

另外,對于采用前面所述的雙線信號編碼方式,在時序邏輯電路的設計上,可采用在輸入任何有效的數據01和10之前,都先把寄存器設置為00或11中間態的協議。這樣,無論進行何種操作,則時序邏輯中相關的寄存器都只有一個寄存器翻轉,有效地防止了寄存器在數據傳輸過程中的信息泄漏。

4 結 語

智能卡是一種高安全性、高可靠性和復雜的片上系統,具有抗功率分析攻擊、時間分析攻擊和故障分析攻擊的能力,但在一些新型的智能卡攻擊技術下其安全受到巨大的挑戰,例如DPA攻擊。本文針對DPA攻擊智能卡的特點,在智能卡的硬件電路上進行了抗DPA攻擊的設計,采用此設計,再結合一些軟件上的抗DPA攻擊措施,就能構成一個完善的智能卡安全體系結構,能十分有效地保證智能卡免受DPA攻擊。

評論