基于ADSP-TS101的高速數字電路設計與仿真

(4)模擬電路和數字電路部分,是否有各自獨立的地線。

(5)后加在PCB中的圖形(如圖標、注標)是否會造成信號短路。

(6)對一些不理想的線形進行修改。

(7)在PCB上是否加有工藝線,阻焊是否符合生產工藝的要求,阻焊尺寸是否合適,字符標志是否壓在器件焊盤上,以免影響電裝質量。

(8)多層板中的電源地層的外框邊緣是否縮小,如電源地層的銅箔露出板外容易造成短路。本文引用地址:http://www.104case.com/article/188863.htm

2 仿真結果

2.1 不同串行端接電阻的仿真

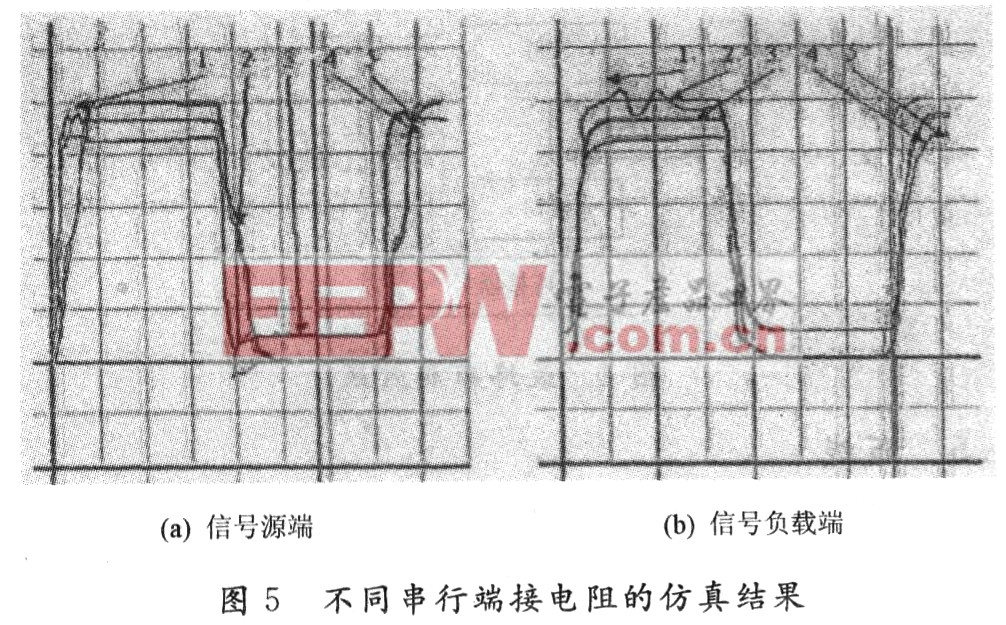

圖5為使用不同的端接方式后的信號源端與負載端的波形,圖5(a)為信號源端的波形,圖5(b)為信號負載端的波形。圖5中,1為未加端接前信號源端與負載端的波形;2為使用串行端接方式(端接電阻50 Ω)后的信號波形;3為使用戴維寧端接方式(上拉電阻100 Ω,下拉電阻100 Ω)后的信號波形;4為使用簡單并行端接方式(下拉電阻50 Ω)后的信號波形;5為使用RC并行端接方式(下拉電阻50 Ω,電容0.1μF)后的信號波形。

由圖5可見,幾種阻抗匹配的端接方式都能不同程度地抑制了信號的反射,說明在存在較大反射的電路中使用合適的端接方式能夠收到很好的效果。

2.2 鏈路口仿真

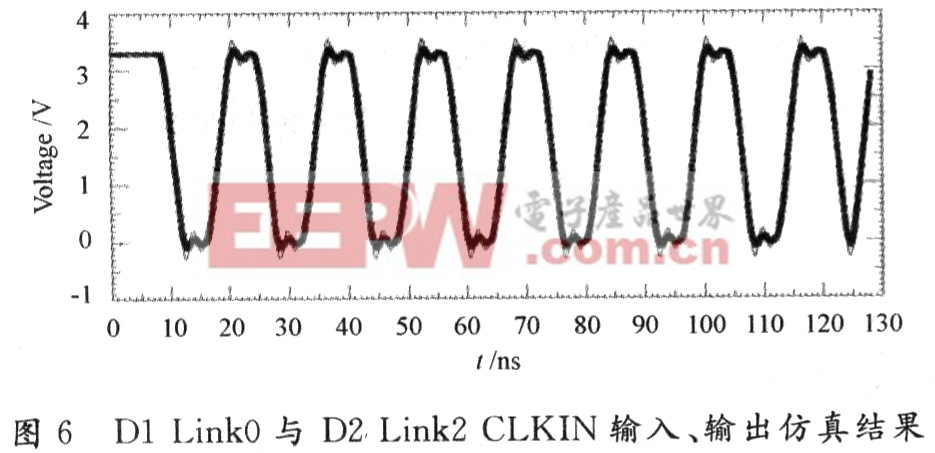

第一組:TS101 D1 Link0和TS101 D2 Link2連接LCLKIN信號,該信號印制線較長且速度要求較高(LAY 7層)。

測試條件:輸入同步脈沖序列1010-1010-1010-1010,頻率125 MHz,抖動10 ps,該序列為模仿CLKIN時鐘信號得到的信號波形,如圖6所示。

圖6中加粗部分為輸入,細線為輸出。由圖可知,信號基本保持了完整性,上升沿和下降沿的單調性未發生改變。雖然仿真頻率高達125 MHz,但是波形的完整性保持完好。

第二組抽取Lay 6層的Link走線最長的一組進行分析,以D4 Link3和D8 Link3的連接為例。思路同上,仿真波形如圖7所示。

情況比Lay 7層稍差,但過沖在420 mV左右,滿足條件。

3 結 語

隨著高速數字電路的發展,PCB密度、速度的提高,以及工藝方面的限制,信號完整性及電磁兼容問題會越來越突出,但只要依據一定的設計準則,通過仿真軟件,可以把高速設計中的問題解決好。

評論