ADS8323與高速FIFO接口電路的CPLD實現

3.1 AD轉換控制與FIFO寫控制模塊

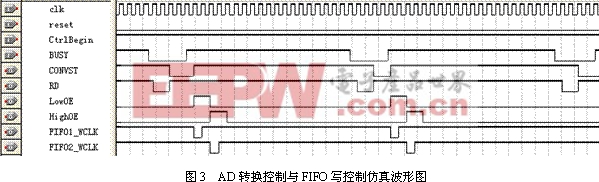

根據ADS8323與FIFO的使用說明,該模塊的工作過程如下:在系統啟動信號CtrlBegin有效之后,啟動AD轉換信號(/CONVST置低);在轉換過程中,將數據緩沖區(由CPLD內部實現的一個16Bit的存儲器)中的前一次轉換結果寫入FIFO中,具體來說,首先使低8位數據使能信號LowOE置高,低8位數據被放到數據總線上,然后產生低8位FIFO的寫時鐘信號FIFO1_WCLK,這樣轉換結果的低8位就被存入低8位FIFO中,按同樣的過程再把轉換結果的高8位存入高8位FIFO中;在轉換結束后(BUSY為低),將AD的讀使能信號/RD置低,于是本次AD的轉換結果被寫入數據緩沖區;完成一次操作之后,再啟動AD轉換信號,開始下一次轉換過程,周而復始,直到系統啟動信號CtrlBegin無效。

該模塊可由狀態機加以實現。在設計中,我們采用Verilog HDL語言編寫,其仿真波形如圖3所示。

3.2 FIFO讀控制模塊

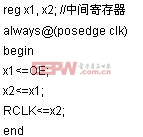

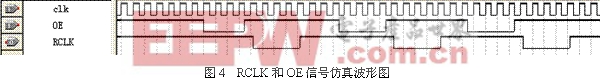

當FIFO中的數據達到一定深度之后,MCU就需要通過該模塊向FIFO讀取數據。該模塊主要產生四個信號,即低8位FIFO的RCLK和OE(定義為RCLK1和OE1)、高8位FIFO的RCLK和OE(定義為RCLK2和OE2)。以往的設計方案是采用兩個獨立的讀地址分別作為RCLK和OE,這種方式雖然操作簡單,但需要兩個讀周期才能完成一次讀操作,這樣大大降低了工作效率。本文采用一個讀地址作為OE信號,再利用對OE的延時信號作為RCLK信號,這樣只要RCLK信號的產生介于兩次OE之間,就能實現用一個讀周期完成一次讀操作,這樣便大大提高了MCU的工作效率。延時模塊由Verilog HDL語言實現,其代碼如下:

仿真波形如圖4所示。

4.結束語

本文采用CPLD實現了AD芯片、高速FIFO存儲器以及MCU之間的接口電路。實驗表明,該電路工作穩定可靠,且通用性強,易于移植到其它數據采集系統中。同時,QuartusII等嵌入式技術的使用,簡化了開發流程,提高了設計效率。目前,該電路已成功應用于某數據采集系統中。

評論