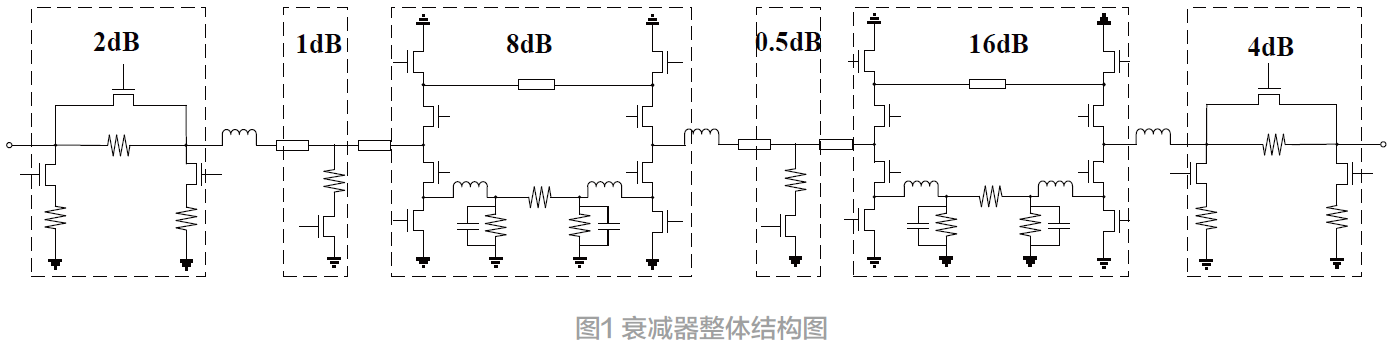

一種中速高精度模擬電壓比較器的設計

2.2 比較器第一級的結構

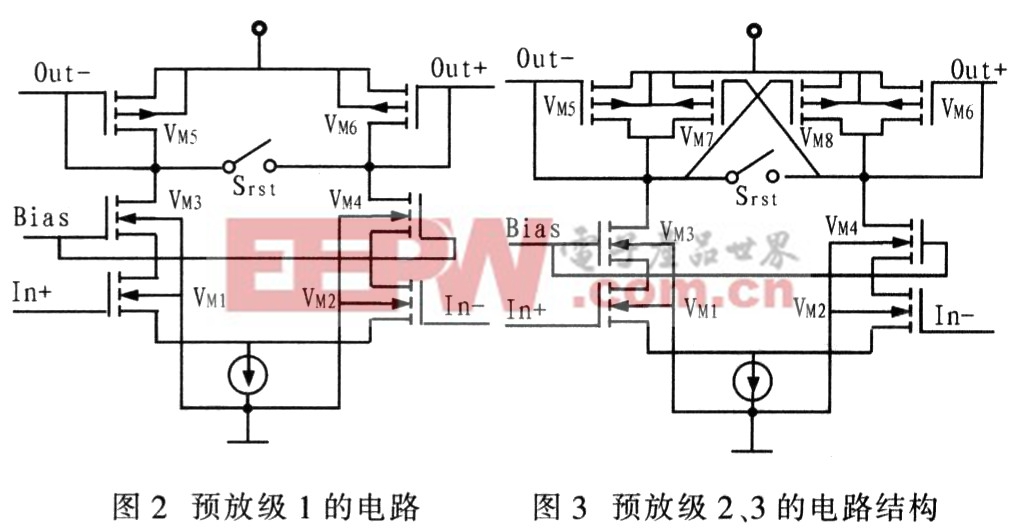

由于第一級前置放大器需將0.2 mV的小信號輸入迅速放大,同時采用輸出失調存儲的失調校準技術,這就要求它具有高帶寬和低增益特點。因此,預放級1可以采用二極管連接成PMOS作負載的差分運放結構,同時考慮本級也是整個高精度模擬電壓比較器的輸入極,它的噪聲性能也對比較器的精度有影響,因此輸入則采用共源共柵(Cascode)的結構,這可將回程噪聲減小gm3,4/gm5,6倍,這在比較器一端固定電位,另一端作輸入應用的情況下尤其重要,最后再加入一個源隨器作為輸出級,既可調節后級放大器的輸入直流電平達到最佳值,又可起到隔離的效果改善噪聲性能。預放級1的電路如圖2所示(后接的源隨器未畫出)。

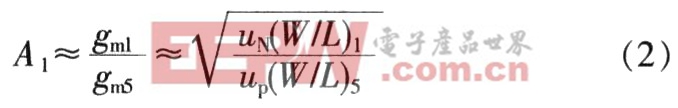

假設電路是完全對稱的結構,則整個電路的增益A1約為:本文引用地址:http://www.104case.com/article/188689.htm

該值一般都在10以下,考慮到帶寬要求和電容上失調電壓飽和的問題,最終確定其取值約為5。同時,在輸出端Out+與Out-之間加入復位開關,在每個比較周期的最初,由復位信號控制開關閉合。將預放級1復位,加快比較速度。

2.3 比較器第二、三級的結構

預放級2與預放級3采用相同的電路結構,為了增加放大器的增益,它在預放級1的電路基礎上加入了2個交叉的PMOS管VM7、VM8,在電路中引人了弱正反饋機制,但縮減了帶寬。由于預放級2的輸入信號比預放級3小。設計時也可適當增大預放級2的電流,有助于提高比較速度。其電路如圖3所示(后接的源隨器未畫出)。

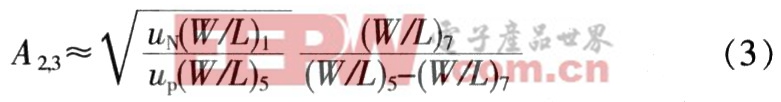

同樣假設電路是完全對稱的,則通過弱反饋補償后,電路的增益約為:

需要注意的是,遲滯比較器也是采用如圖3所示的電路結構,所不同的是遲滯比較器使用了強正反饋機制。兩者的區別就在于交叉的PMOS管VM7、VM8引入的電流相對于PMOS管VM5、VM6的電流的大小不同。當PMOS管VM7、VM8的電流大于PMOS管VM5、VM6的電流時,整個電路呈正反饋狀態;反之,電路中的正反饋不足以抵消負反饋,整個電路呈負反饋狀態。由于電路在大信號分析中PMOS管VM5~VM8的過載電壓是相同的,因此它們的電流和寬長比成正比,故VM5的寬長比一定要大于VM7的寬長比才能實現弱正反饋。

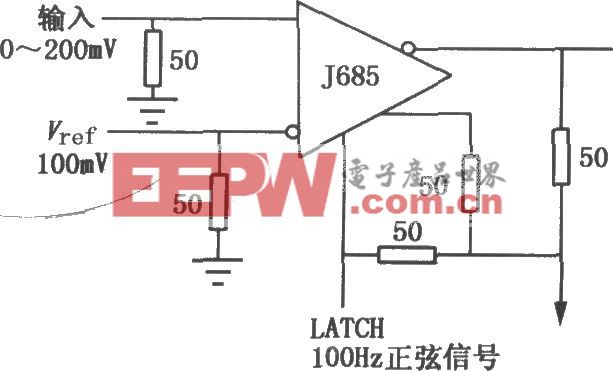

2.4 鎖存比較器與數字觸發電路

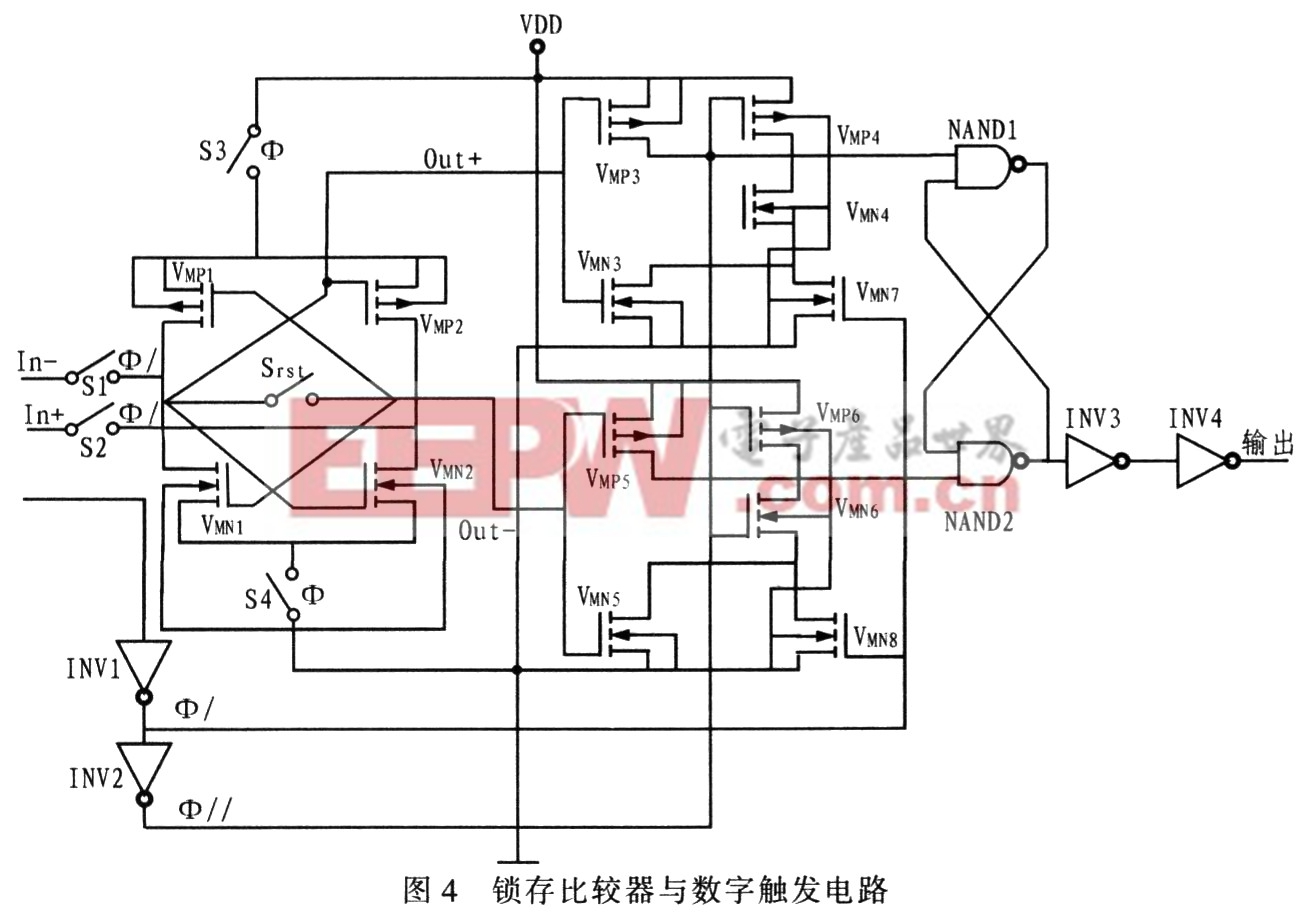

鎖存器實際上就是2個反相器首尾互連,由于利用反相器的正反饋的機制,輸出信號與時間呈正指數關系變化,因此可將輸入的小信號差量迅速放大到數字可識別的電平。同時,鎖存器具有低功耗特點,因為它在一段時間內是不工作的,此時干路的開關被切斷,因此無電流,功耗降低。然而,正是由于這樣的工作特點。使鎖存器工作時的輸出狀態并未持續一個時鐘周期,為了串行數字輸出正確以及給D/A轉換器提供正確的置位信號,再生放大器后面應加適當的觸發電路,以便在再生放大器工作期間正確輸出持續時間為一個周期的比較結果。因此,設計出如圖4所示的電路。

當φ為低電平時,輸入信號In+和In-與鎖存器接通,而鎖存器與電源、地相連的開關均斷開,鎖存器處于感應輸入信號階段;同時,在數字觸發電路中,高電平φ/使得開關管VMN7、VMN8導通接地,此時,低電平φ//分別通過VMP4、VMN4組成的反向器和VMP6、VMN6組成的反向器分別到達2個與非門的輸入端并將其值置為高電平1,使得后級的數字RS觸發器呈保持狀態,持續保持輸出不變。

評論