高速數模轉換器TQ6124的原理與應用

TQ6124是一種高速高精度的數模轉換器芯片。它具有14位數據位并采用分段結構將數據位分成最高4位、中間3位和最低7位。TQ6124可對各段的數據采用不同的數模轉換方法,其內部集成有高精度的電流源和高精度電阻,以保證數模轉換的精度。TQ6124轉換速度可達到1GSa/s。該芯片設計靈活,使用方便,只需增加一、二塊集成電路和少量的外圍電路,即可構成一個完整且性能很高的數模轉換器。

2 TQ6124的結構特點及引腳功能

2 .1 TQ6124的結構

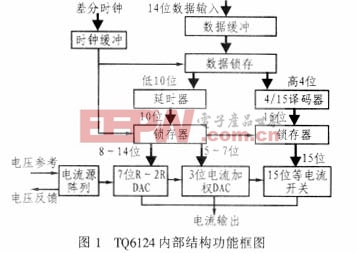

TQ6124主要由鎖存器、編碼器、延時器、電流源、電流開關陣列、R~2R電阻網絡等電路組成。圖1所示是其內部結構框圖。TQ6124的主要特點如下:

●數模轉換速率高達1GSa/s;

●具有14位數據位;

●具有1G的模擬信號帶寬;

●輸出可直接作為射頻的前端;

●時鐘和數字數據為ECL電平;

●采用44腳QFP封裝。

2.2 TQ6124的引腳說明

圖2為TQ6124的引腳排列圖,各引腳的功能說明如下(括號中的數字為引腳號):

Vss(1、11、12、33、34、44):數字電源輸入端,通常接-5V。電源濾波的旁路電容應盡可能靠近電源腳,并直接連接到地;

VAA(21、23、24):-12V模擬電源輸入端;

DGND(6、7、8、28、29、37、40):數字地;

AGND(13、15、18、19):模擬地;

D13~D0:數字信號輸入端,其中D13為數據最高位,D0為數據最低位;

CLK、NCLK(9、10):差分時鐘輸入端;

IREF(14):參考電流輸入端,直接連接到模擬地,是開關陣列的虛擬電流源;

VSNS(20):判斷電壓輸出端,芯片正常工作時有輸出,且Vsns=VREF;

VREF(21):電壓基準輸入端,一般設計為-9V,當VREF=-9V時,輸出的模擬信號峰-峰值為1V;

Midtrim(25):調整中間數據位的電壓輸入端,以調整波形,可選;

Lsbtrim(26):調整低位數據位的電壓輸入端,以調整波形,可選;

ECLref(27):可選的ECL電平參考電壓輸入端,當數字數據和時鐘為ECL電平時,該腳懸空,芯片內部可產生-1.34V的電壓。

3 TQ6124的外圍電路設計

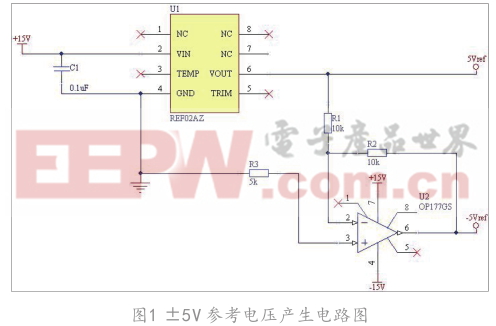

TQ6124使用靈活方便,只需一塊電壓基準芯片和一塊運算放大器及少量的外圍電路即可(如圖3所示)。這兩塊集成電路的主要用途是為數模轉換芯片提供參考電壓。在數模轉換器中,參考電壓的精度、穩定性和抖動對所產生的模擬信號的精度、穩定性和抖動有很大的影響。特別是該芯片具有的14位的數據位對參考電壓的性能更加敏感。AD586為AD公司生產的電壓基準芯片,它性能好,誤差峰-峰值只有4μV,可以滿足TQ6124的14位精度的參考電壓要求。該電壓基準(AD586)的輸出與芯片的反饋輸出VSENSE通過運算放大器MC34071可構成負反饋電路,以將VREF穩定在-9V,因而可進一步減小外部電源細微變化對其所造成的影響,從而保證輸出模擬信號的精度和穩定性。

評論