高幀頻CCD數據采集處理系統的設計

3.2.2 ADC控制信號

AD9942內部寄存器由6條外部配置線進行寫入,分別為兩條32位數據線SDATA_X(SDATA_A,SDATA_B)包括8位地址、24位數據(用于AD工作狀態控制);兩條位同步信號SCK_X(SCK_A、SCK_B);兩條控制有效信號SL_X(SL_A、SL_B)。數據信號在A/D變換前,即幀同步和行同步信號開始前,SL―X為低電平時由FPGA寫入A/D寄存器,并控制其工作狀態。仿真時序圖如圖5所示。本文引用地址:http://www.104case.com/article/188517.htm

3.2.3 FPGA實現數據緩存

經過A/D器件轉換之后的數據,首先通過FPGA內部高速緩沖,然后再轉存到片外存儲器中。該系統中FPGA內部Block RAM陣列的控制采用乒乓傳輸結構,它可以保證采樣和傳輸各自不間斷的進行。具體做法是將96個:Block RAM分成兩組(RAM1,RAM2),時鐘和控制信號均獨立。系統工作時,輸入數據分為兩路,流向由VHDL語言編程控制寫地址來實現RAM1和RAM2的選擇,當地址指向第一組的48塊Block RAM時,RAM1進行數據寫入,與此同時,第二組的48塊BlockRAM則進行數據讀出;RAM1存儲結束后,切換到RAM2寫入而RAM1讀出的模式,如此循環。

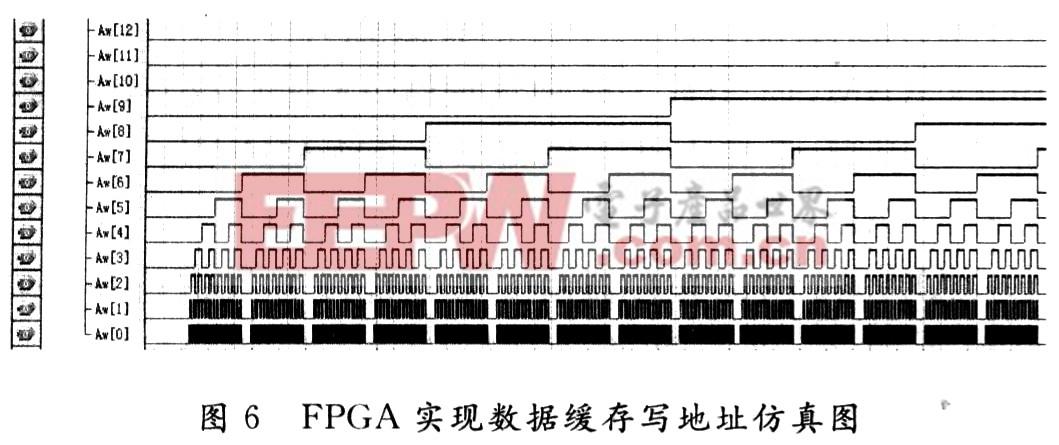

XQ2V3000每一個Block RAM的容量為18 Kb,總容量為1 728 Kb(18 Kb×96),CCD輸出的一幀圖像數據量為1 572.864 Kb(256行×512列×12 b),可見完全可以實現幀存儲。具體實現時由RAM1和RAM2各存取半幀圖像,用VHDL語言在對讀/寫地址進行編程時,計數器計數滿128行數據后,讀/寫地址分別指向另一個RAM,部分寫地址仿真圖如圖6所示。

最終經過對AD9942的各項控制信號和FPGA數據緩存地址的仿真,仿真結果正確并符合技術手冊的各項要求。

4 結 語

這里介紹了一種基于FPGA控制的CCD高速數據采集處理系統的原理和實現。由于創新性的將系統控制和數據緩存集成在一片FPGA內,并將多路CCD模擬信號通過分時復用一片AD9942實現了模/數轉換。從而提高了系統的集成度,而且采用FPGA完成整個系統的主體設計具有速度快、設計靈活、保密性好和維護方便等優點,有效地解決了全系統控制同步問題。通過仿真結果測試,該系統可以穩定的工作,A/D轉換速率可以達到40 Mb/s,幀頻實現300幀/s,可以為CCD應用向高速、小型化、智能化、低功耗方向發展提供借鑒意義。

評論