零延時隔離技術的RS485息線節(jié)點設計

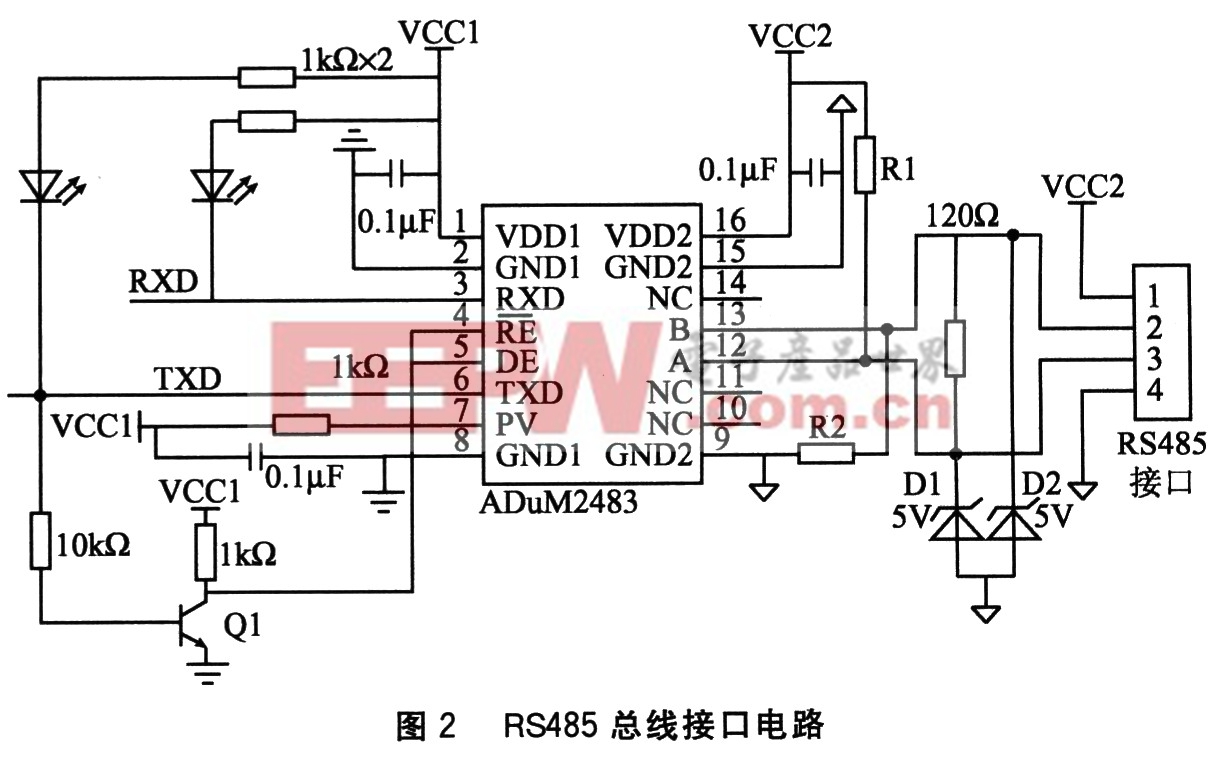

ADuM2483獨具的PV(Power-Valid)電源監(jiān)控功能,可根據(jù)供電電源的穩(wěn)定情況而開斷芯片工作。為了避免GND1緩慢上電/掉電(>100 μs/V)引起的A、B輸出抖動情況,ADuM2483設計了PV引腳。當電平低于2.0 V時,此引腳為低,芯片不工作;高于2.3 V時,此引腳為高,芯片正常工作。D1與D2用來防止總線上的瞬變干擾。RS485總線接口電路如圖2所示。本文引用地址:http://www.104case.com/article/188465.htm

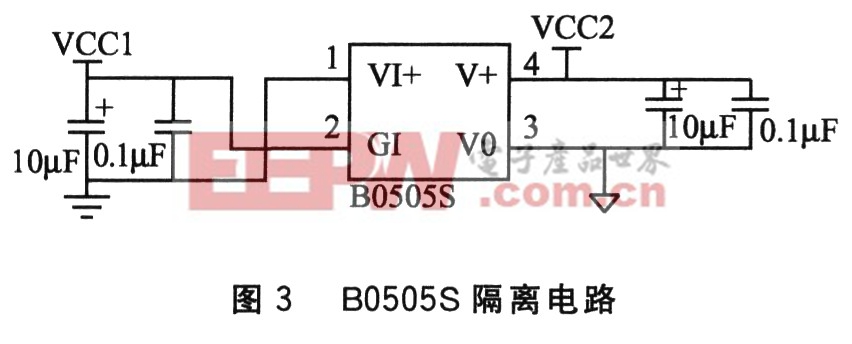

采用金升陽公司的B0505S隔離模塊實現(xiàn)收發(fā)器兩端電源與地完全隔離。其隔離電路如圖3所示。

4 RS485總線零延時收發(fā)的實現(xiàn)

在RS485總線節(jié)點電路設計中,一般要將收發(fā)器的接收允許(RE)和發(fā)送允許(DE)兩個引腳短接,由一根信號線來控制收發(fā)的切換。在控制電路中,一般用單片機I/O引腳來控制RS485收發(fā)器的收發(fā)轉換,這樣就需要由軟件來控制單片機I/O引腳的電平,以達到控制RS485收發(fā)轉換的目的。RS485收發(fā)器通常處于接收狀態(tài),當要發(fā)送數(shù)據(jù)時,由程序控制RE/DE變?yōu)楦唠娖剑型ㄐ艈卧l(fā)送數(shù)據(jù);等待發(fā)送完畢后,程序再將RS485收發(fā)器轉換到接收狀態(tài)。發(fā)送完畢的標志一般由串行通信的特定寄存器提供狀態(tài)指示,再由程序去查詢。這樣造成RS485通信存在以下問題:

◆在想要發(fā)送數(shù)據(jù)和真正能發(fā)送數(shù)據(jù)之間,存在一定的延時;

◆如果發(fā)送到接收的轉換時機不當,則會造成數(shù)據(jù)丟失;

◆在接收和發(fā)送數(shù)據(jù)轉換期間,容易引入干擾,收到多余的雜亂數(shù)據(jù)。

在設計RS485總線接口電路時充分考慮到了總線的延時問題,應用一個高速的NPN三極管控制實現(xiàn)RS485總線的零延時收發(fā),如圖2所示。

不發(fā)送數(shù)據(jù)時,邏輯端TXD信號為高電平。此時Q1導通,使RE/DE信號線上為低電平,ADuM2483接收允許。發(fā)送數(shù)據(jù)時,若TXD為低電平,Q1關斷,從而使RE/DE信號線上為高電平,發(fā)送允許,ADuM2483的輸出端A、B上產生表示低電平的差分信號。當TXD為高電平時,Q1導通,使RE/DE信號線上為低電平,ADuM2483的A、B端處于高阻態(tài)。此時靠電阻R1和R2的上拉和下拉作用,使總線上產生正的差分信號,從而將TXD的高電平信號送出。

由以上分析看出,在使用這個電路時,只要程序能保證不同時進行接收和發(fā)送的操作,即保證是半雙工傳送數(shù)據(jù),則不必用軟件控制RE/DE進行接收和發(fā)送的轉換,可由硬件本身完成,從而提高了RS485總線接收、發(fā)送數(shù)據(jù)的高速率和高可靠性。

結 語

本節(jié)點的設計采用新型集成隔離電路的RS485總線收發(fā)器ADuM2483,降低了系統(tǒng)的功耗,簡化了設計的結構,增強了系統(tǒng)的穩(wěn)定性。采用硬件的零延時技術提高了節(jié)點的收發(fā)效率,提高了系統(tǒng)性能。經測試,效果良好,抗干擾能力強,特別適合工業(yè)控制場合的應用。

評論