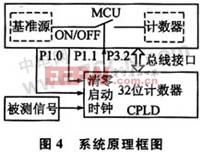

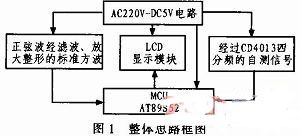

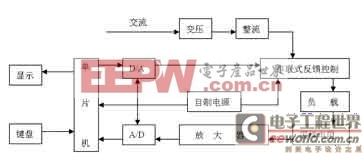

一種高性價比等精度數字頻率計方案設計

2.2單片機與CPLD接口設計

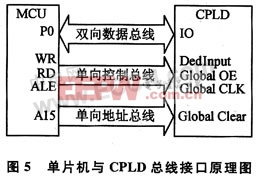

圖5所示為一種基于總線的接口方案,采用三總線(數據、控制、地址)結構,用于實現單片機與CPLD之間的數據傳輸。

單片機P0口為雙向數據總線,與CPLD的通用IO口連接,完成數據和低8位地址傳送。控制總線包括單片機讀寫控制總線RD和WR,以及地址鎖存信號ALE(Address Lock Enable)。地址總線A15(P2.7)通過CPLD的全局輸入信號引腳輸入。

2.3 CPLD電路

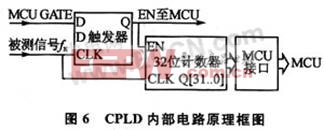

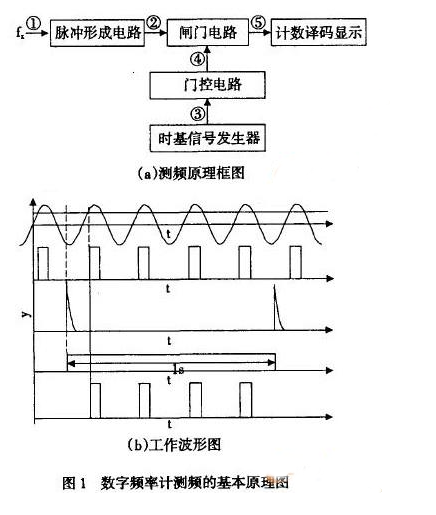

CPLD內部電路原理框圖如圖6所示。當預置閘門GATE輸入高電平時,由于DFF觸發器為邊沿觸發器,在上升沿時才將數據輸出,所以Q輸出端并不立即置1,只有當外部信號上升沿到來時,Q才為1,使能計數器和定時器。這樣保證了計數器和定時器在被測信號的上升沿到來時同時有效。當預置閘門GATE=0關閉時,兩計數器的允許信號同樣在被測信號的上升沿到來時同時關閉。由于基準信號的定時器與被測信號嚴格同步,所以理論上最大誤差只有基頻的一個周期。CPLD內計數器為32位,在預置時間內,只要計數器不溢出,即可準確測量被測信號個數。

3方案實現

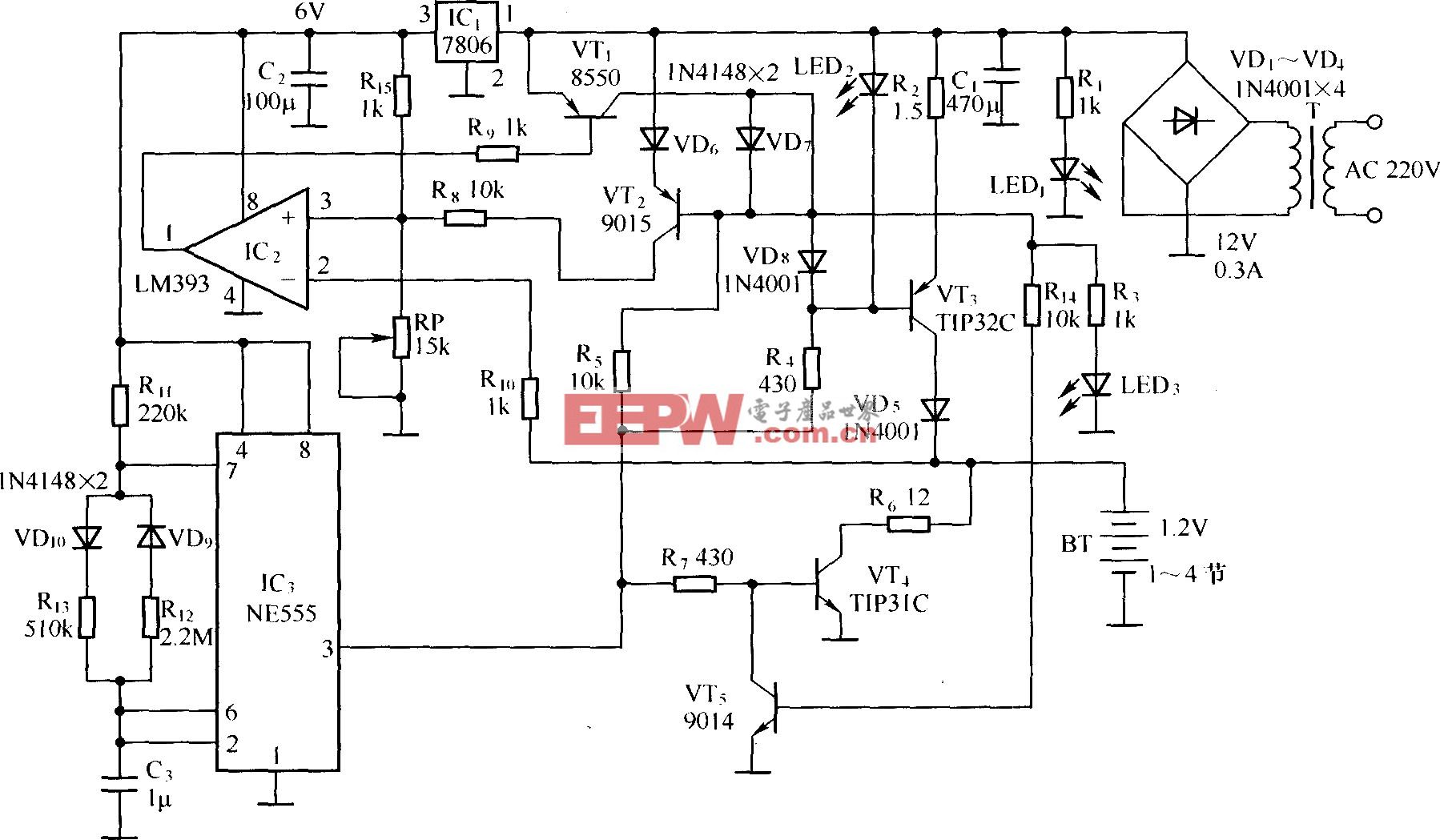

3.1電路原理

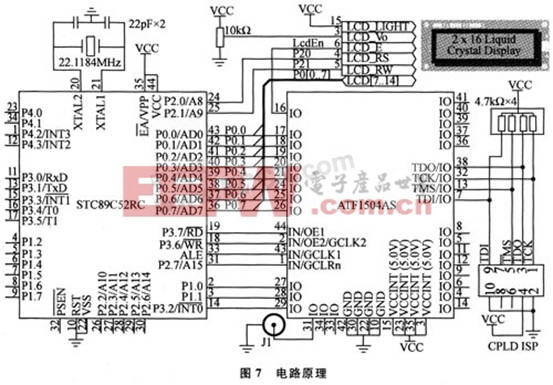

電路原理如圖7所示。圖中給出了單片機(STC89C52RC)與CPLD(ATF1504AS)的具體接口電路,LCD1602接口電路,帶ISP下載接口的CPLD電路,被測信號從J1直接輸入給CPLD I/O引腳。這里沒有給出信號前置調理與波形整形電路。

3.2 CPLD電路設計

CPLD開發選擇Altera公司的EDA軟件QuartusII和目標器件EPM7064SLC44=10,需要完成電路設計輸入、編譯、仿真、引腳綁定(引腳分配請參考電路圖),并編譯得到最終配置文件*.pof。然后再使用Atmel公司提供的轉換工具POF2JED軟件將前面得到的*.pof文件轉換成*.jed文件,再用AtmelISP軟件將*.jed文件下載到CPLD器件ATF1504即可。

評論