具有PCI和并行接口的數據采集系統設計

A/D轉換芯片使用的是ADI公司的AD6644。AD6644是高速、高性能的14-bit65MSPS單片模數轉換器,內部自帶采樣保持器和參考電壓電路,可以提供完整的轉換應用解決方案。AD6644是ADI公司Softcell接收器芯片組中的一個代表芯片,它是專門為第三代移動通信系統設計的ADC芯片,特別適用于多通道、多模式接收機應用。同其它芯片相比,由于在奈奎斯特頻率范圍內,AD6644的無雜散動態范圍指標超過了100dB,大大增強了從輸入端雜散分量中檢測有用小信號的能力,使它更加適用于多模式的數字接收機。同時,AD6644的信噪比的典型值也達到了74dB。AD6644還可以應用于單通道數字接收機中,如寬通道帶寬系統中,能夠精確變換寬帶模擬信號(200MHz輸入帶寬)。通過欠采樣,可以將諧波成分分配到有用頻帶之外,配合使用數字下變頻芯片可降低有用信號帶寬內的噪聲平臺。

2.4 時鐘產生模塊

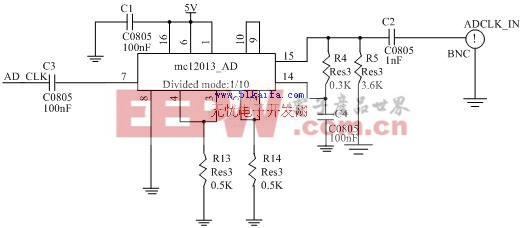

圖4 雙模前置分頻器MC12013工作原理圖

本采集系統的時鐘是通過外部晶體振蕩器或者時鐘信號發生器產生,然后經過前置分頻后加到FPGA的專用時鐘引腳輸入端,并使用FPGA中的全局時鐘網絡布線。我們采用雙模前置分頻器MC12013進行前置分頻。MC12013是超高速雙模前置分頻器,雙極型發射極耦合晶體管邏輯。模數比為10/11,由模式控制電平的高低決定分頻比。MC12013是ECL集成電路,最高工作頻率可達550MHz,并帶有一個內部的ECL到TTL的轉換電路。當變模控制端輸出高電平“1”時,雙模前置分頻器按低模分頻比M工作;當輸出低電平“0”時,按高模分頻比M+1工作。這里只使用除10分頻功能,工作原理圖如圖4。

2.5 接口部分設計

本系統中使用了2種接口方式,即DB25并行接口和PCI總線接口。雖然2種接口的作用都是將經過模數轉換模塊采集后并存儲到FPGA中的數據傳輸至PC機中,但是2者的工作過程卻是不同的。

當使用DB25并行接口傳輸數據時,由于并行接口傳輸率的限制(EPP工作模式下只能達到1MBps左右),因此當A/D轉換器進行高速采樣時(如AD6644工作在50MHZ下),并行接口沒有能力在相同的時間里把ADC存放到FPGA中的數據完全讀取出來。所以此時不能實現實時傳輸,只能讓系統工作于存儲轉發的狀態下,即當ADC中的采集數據將FPGA中RAM存儲器寫滿時,停止數據采集工作,進而轉向數據讀取過程,待DB25將FPGA存儲器中的數據完全傳輸至PC機之后,再重新啟動ADC的數據采集過程,如此反復直到全部數據采集、存儲并轉發完畢。

當使用PCI總線接口傳輸數據時,由于PCI接口的傳輸率很高(本系統中使用33MHZ*32bit的傳輸模式),因此即使當A/D轉換器進行高速采樣時,PCI接口仍然有能力在相同的時間內將ADC存放到FPGA中的數據讀入到PC機中。所以此時可以在一定程度上實現實時數據采集和存儲。

3 FPGA與PC端控制軟件設計

Altera公司的FPGA產品與其它公司產品的最大區別是它采用連續式的互連結構,即采用同樣長度的一些金屬線實現邏輯單元間的互連。連續式互連結構消除了FPGA分段式互連結構在傳輸延時上的差異,在邏輯單元間提供快速、具有固定延時的通路。這種結構的優點是布線速度快且易于仿真,在實現復雜大型設計時,可以縮短開發周期。開發Altera公司的可編程邏輯器件有兩種軟件,QuartusII和MAX+PLUSII。本設計采用QuartusII開發軟件,其提供了一種與結構無關的全集成化設計環境,使設計者能對Altera的各種產品系列方便地進行設計輸入、快速處理和器件編程。QuartusII開發系統具有強大的處理能力和高度的靈活性。

在本系統中,FPGA起到的是一個控制橋梁和傳輸橋梁的作用,通過來自于PC主機的控制信號和傳輸信號,來有序的控制ADC的采樣,數據的存儲和傳輸過程。而如何決定整個系統開始工作的時間,采用何種接口的傳輸模式,數據在PC機中的存儲方式以及如何利用采集后的數據來顯示原始波形,這些任務都是由安裝在PC端的控制軟件所完成的。

我們通過VB程序實現了這個控制軟件。在Windows環境下,數據采集系統作為外部設備,我們將通過調用動態鏈接庫(TVicHW32.DLL)來完成對其的讀寫操作。TVicHW32.DLL可以對內存、I/O端口、中斷等進行直接控制和讀寫,這里我們使用其部分功能和函數。

本文作者創新點:

本文所設計的方案,就是將FPGA作為整個數據采集系統的控制核心和傳輸橋梁。一方面可以根據上位機的指令來完成對整個系統工作模式和狀態的精確時序控制,另一方面可以通過FPGA中豐富的宏功能塊資源和可嵌入的IP核資源來實現高速緩存和高速數據傳輸接口。

評論