高速雙通道采樣芯片AT84AD001B及其應用

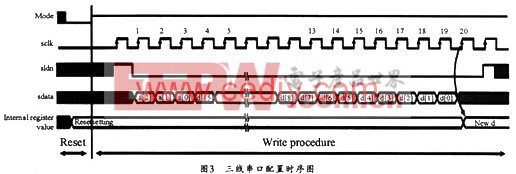

AT84AD001B高速模數轉換器芯片的MODE、CLK、LDN及DATA 4個引腳可用于三線串口的配置。其中MODE引腳用于配置選擇是否啟用三線串口,MODE為高時啟用三線串口,為低時屏蔽,參數為缺省狀態。CLK是三線串口的配置時鐘輸入引腳。LDN為配置通過三線串口配置寄存器的開始和結束信號輸入引腳。DATA為三線串口的寄存器配置數據輸入引腳。CLK引腳允許輸入的最大時鐘頻率是50 MHz。三線串口配置時序見圖3所示。

在對AT84AD001B高速模數轉換器芯片的應用電路進行設計時,可以通過微處理器對三線串行接口進行配置。通常在高速信號處理系統中通過后端做信號處理的高速FPGA對三線串口進行配置,而無需添加專用芯片,因此可以節省空間,利于PCB設計。系統啟動或復位后,當MODE腳為高電平,LDN腳為低電平時,DATA腳將會在每一個CLK的上升沿輸入1 bit數據。由于每個三線串口寄存器需輸入的配置數據包括3 bit的寄存器地址和送入該寄存器的16 bit數據,因此該設計總共需配置8個寄存器,表1是各寄存器的配置參數。

5 AT84AD001B的工作模式

AT84AD001B的工作方式按輸入的模擬信號來分,具有以下三種模式:

(1)I通道與Q通道有相互獨立的兩路輸入;

(2)I通道與Q通道均使用I通道的模擬輸入;

(3)I通道與Q通道均使用Q通道的模擬輸入。

AT84AD001B的工作方式按時鐘輸入也可以分為三種:

(1)I通道和Q通道有各自獨立的時鐘,分別在上升沿時采樣;

(2)兩個通道都使用I通道時鐘,在I通道時鐘的上升沿采樣;

(3)兩個通道都使用I通道的時鐘,ADC內部產生一個同頻反相的時鐘作為Q通道工作時鐘。在第3種模式下,當兩通道輸入同一模擬信號時,就可以實現交替式并行采樣。ADC的采樣速率為輸人工作時鐘的2倍。

AT84AD0001B的工作方式有多種選擇,用戶可以根據自身系統的需要和特點來選擇最合適的工作模式。

6高速采樣設計

采用AT84AD001B和高速FPGA來實現采樣系統的設計應遵循兩個原則:一是要有足夠的專用LVDS差分邏輯接收通道:二是用作AD輸出差分數據接收的專用LVDS差分邏輯接收通道的最高數據傳輸速率要大于AD的數據輸出速率。

本設計中的AT84AD001B與高速FPGA的接口設計如圖4所示。

圖中FPGA用于產生AD的時鐘和三線串口配置信號,由于AD的采樣輸出信號速率很高,設計中需要通過串并轉換或數據抽取使數據速率降低之后,才能對信號進行處理,而不宜直接做信號處理。

7結束語

由于AT84AD001B的工作方式靈活多樣,所以基于它的高速采樣系統的設計也很靈活,因此可以根據目標系統的需求或指標來滿足系統的設計要求。而且,AT84AD001B的這種靈活性也方便了它在其他領域中的推廣。

評論