數字式超聲波探傷儀中高速數據采集模塊設計

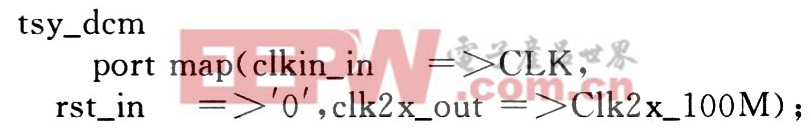

數字時鐘管理單元(DCM)是FPGA內部管理、掌控時鐘的專用模塊,能完成分頻、倍頻、去抖動和相移等功能。通過FPGA的DCM可以很方便地對AD9446的時鐘輸入信號進行掌控。在實際電路中需要注意的是要做到DCM倍頻輸出的時鐘信號與AD9446的時鐘輸入信號保持電平匹配。

下面給出調用DCM后時鐘輸出的VHDL語言描述:

2.3.2 數據壓縮

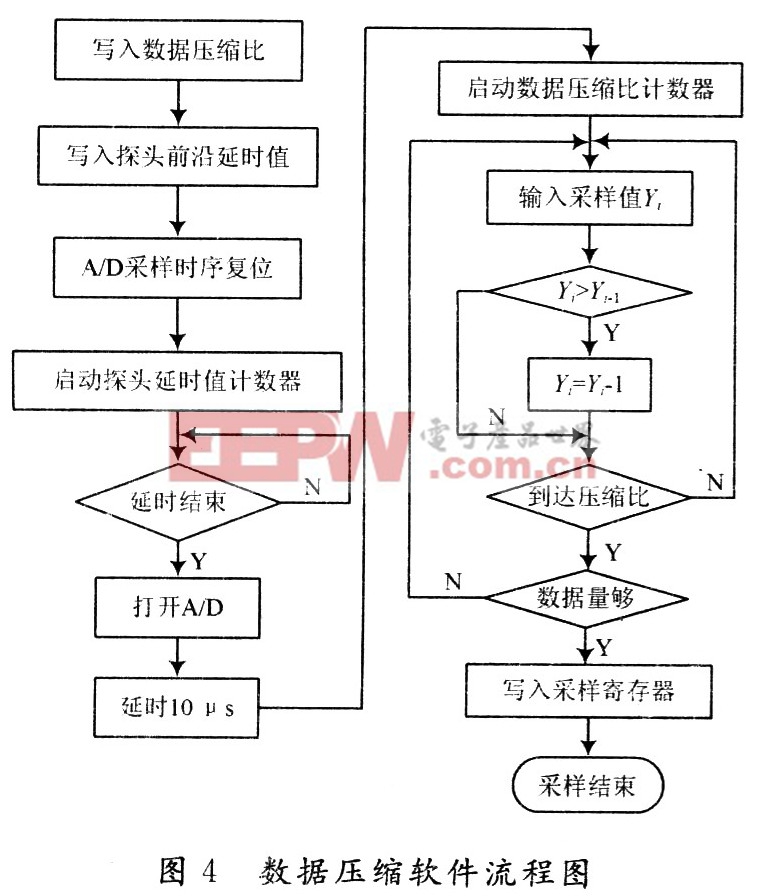

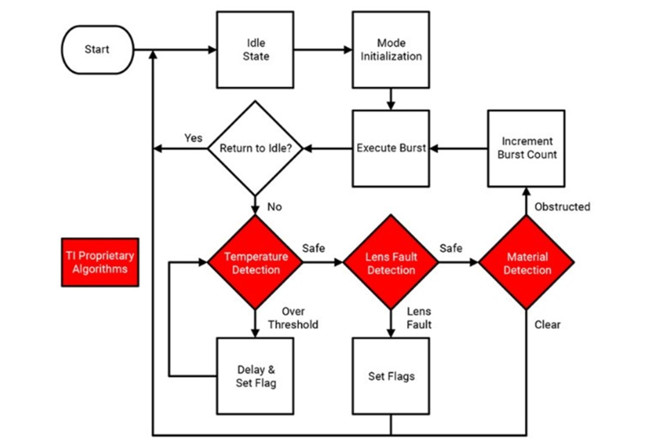

數據壓縮處理是對射頻信號高速采樣后進行前置處理的重要環節之一,需要在保持超聲回波信號基本特征前提下對采樣數據進行在線壓縮,而且要求壓縮后的數據與原始采樣信號的包絡相吻合。為此,在每次壓縮過程中,只取采樣所得的最大值,而舍棄其他采樣值。FPGA將計算所得采樣數據的壓縮比、探頭前沿延時計數值等數據送入相應的鎖存器,然后發出時序復位命令并發射,啟動探頭延時計數,延時到后啟動A/D采樣,同時壓縮比計數器開始計數,在時鐘信號的控制下,每采樣一次,壓縮比計數器減1,并將當前采樣值與前次采樣值比較,如大于則保存,否則舍棄,直至壓縮比計數到零后,得到一個有效的采樣數據。同時壓縮比計數器自動復位,重新開始計數,其工作流程如圖4所示。

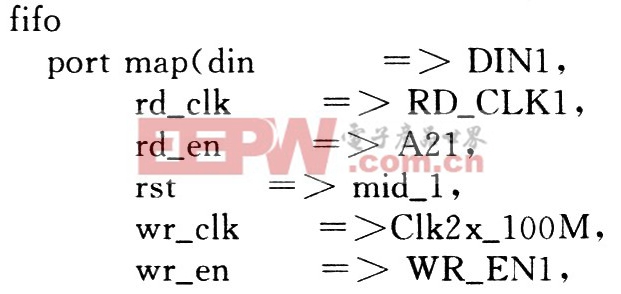

2.3.3 數據緩沖

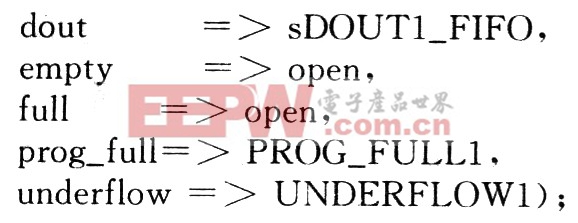

為了解決前端數據采集與后端數據傳輸在速率上的不匹配問題,在FPGA內部設置一塊數據緩沖FIFO,大小為8K×16 b,壓縮后的數據直接存儲到FIFO中,而微處理器對FIFO中數據的讀取通過中斷方式完成。數據緩沖FIFO通過core generator例化,只需要少量的讀/寫控制邏輯就可以使FIFO正常工作,而且FIFO的大小可以在FPGA提供的RAM位數范圍內靈活設置。下面給出例化后的FIFO的VHDL語言描述:

保存在FIFO中的數據通過這些邏輯控制端口便于微處理器對其進行讀取、清零等操作。

3 結語

設計的基于AD9446的數據采集模塊采用FPGA實現數據采集控制、數據壓縮及數據緩沖等功能,簡化了硬件電路,提高了模塊的可靠性和穩定性,并有利于模塊的功能升級。同時采用高速高精度模/數轉換器滿足了數字式超聲波探傷系統對數據采集精度方面的要求。另外,FP-GA對數據進行的預處理,方便了微處理器對數據的調用和后處理。

評論