射極跟隨器輸出電路的靜態(tài)功耗

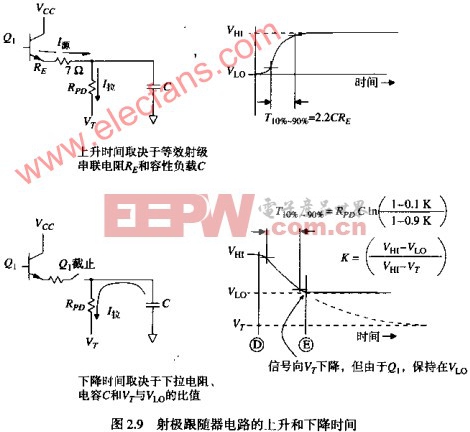

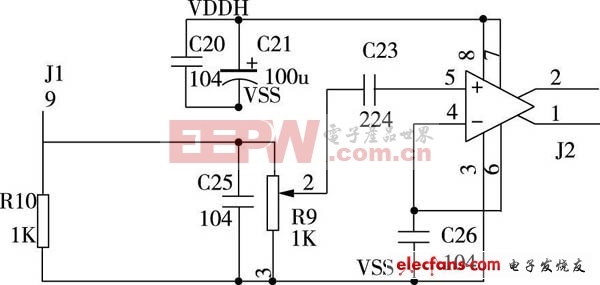

圖2.9舉例說明了一個ECL或GAAS射極跟隨器輸出電路。該電路在HI和LO兩個狀態(tài)都有電流流過。

本文引用地址:http://www.104case.com/article/187948.htm

對于10KH和10G產(chǎn)品系列,兩者的邏輯HI和LO輸出電壓都是相近的,盡管不同的ECL和GAAS射極耦合邏輯系列在溫度軌跡特性上存在細微的判別。這些邏輯電路通常采用-5.2的電源供電。高電平輸出(多數(shù)情況下是正的)標稱值為-0.9V,而低電平輸出為-1.7V。

射極耦合邏輯電路需要有一個下拉電阻,通常用來端接到-5.2V或者中間電壓-2.0V。這里我們介紹一下這兩種情況下的計算。

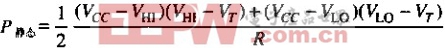

當輸出電壓通過一個戴維南等效電阻R下拉至VT時:

由-5.2V供電的ECL邏輯電路通過電阻R下拉至-5.2V時,代入這些數(shù)值,上式可簡化為:

VCC=0(正電壓)

VHI=-0.9(標稱邏輯高電平)

VLO=-1.7(標稱邏輯低電平)

VT=-5.2(下拉電壓)

P靜態(tài)=4.91/R

同樣的電路通過電阻R下拉至-2.0V時,式

可以簡化為:

VCC=0(正電壓)

VHI=0.9(標準邏輯高電平)

VLO=-1.7(標稱邏輯低電平)

VT=-2.0(下拉電壓)

P靜態(tài)=0.75/R

對于相同的電阻值,使用-2.0V端接時表現(xiàn)出明顯的功耗優(yōu)勢。這是因為當電源電壓被下拉到-2.0V時,下拉電阻汲取電流也較小。小電流意味著低功耗。較小的電流還意味著電路從HI轉(zhuǎn)換到LO時需要更長的下降時間。

由于輸出電路是一個射隨器,上升時間不受下拉電流的影響。圖2.9中標明了10KH系列的ECL邏輯晶體管Q1的發(fā)射極等效串聯(lián)電阻RE的阻值約等于7歐,當給負載電容C充電時,源電流遠大于下拉電流,因此充電時間常數(shù)等于它們的乘積:TRC=REC

TRC是輸出電路從低電平狀態(tài)上升到高電平的63%時所需的時間。上升到高電平的90%所需的時間將是它的兩倍多一點,簡單RC電路的10~90%上升時間是:

該時間常數(shù),見上式,通常小于晶體管Q1的開啟時間,因此輸出電路的上升時間通常等于晶體管Q1的開啟時間。

在下降沿,晶體管Q1截止,不再有電流流過發(fā)射極。只有電容C通過下拉電阻放電,這就是功率和上升時間的關(guān)系開始起作用的地方。下降時間直接與電容C放電的速度成正比。功耗與靜態(tài)下拉電流成正比。不管下拉電阻是連接到-5.2V,都需要一個大電流迅速地將電容C放電。

圖2.9顯示了電流衰減的波形。在D時刻,晶體管Q1截止。輸出電壓在時間常數(shù)RPDC內(nèi)衰減至電壓VT。在E時刻,電壓已降到VLO,而晶體管Q1開始翻轉(zhuǎn),阻止了輸出電壓的進一步衰減,電壓始終保持在VLO。

如果Q1完全截止,從10%到90%的下降時間是:

評論