隨機脈沖信號采集卡的設計

3 系統硬件電路設計

該系統硬件電路主要包括單片機主系統中的隨機脈沖放大及限幅電路、脈沖幅度、脈沖寬度測量電路、高速信號采集及存儲電路及由EPLD等構成的控制信號電路等。

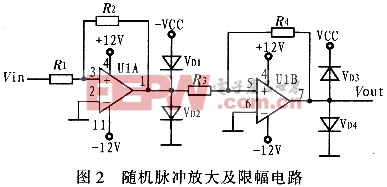

3.1 隨機脈沖放大及限幅電路

隨機脈沖放大及限幅電路完成脈沖信號的放大、限幅及整形,以滿足TTL輸入端信號的要求。圖2為隨機脈沖放大及限幅電路,采用高速運算放大器OPA603,其特點是頻帶寬且轉換速率較高,適用于脈沖放大類電路。輸入的脈沖信號通過兩級放大及限幅后。輸出的脈沖信號送到80C196的高速輸入器件的輸入端。本文引用地址:http://www.104case.com/article/187802.htm

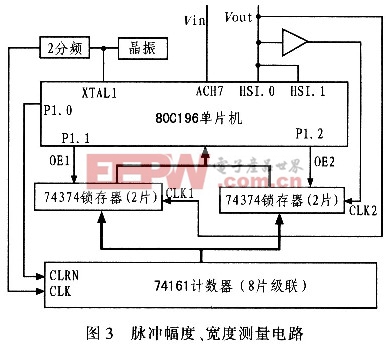

圖3為脈沖幅度及寬度測量電路示意圖。單片機(80C196)內置的10位A/D轉換電路完成脈沖幅度的測量。由74LSl61構成的脈沖計數電路測量脈寬。主系統電路負責整個系統的控制、采樣頻率的設置及相關的數據處理及控制傳送等。其工作原理為:隨機脈沖信號(Vin)送入80C196的模擬信號輸入端ACH6,然后由80C196的內部的10位A/D轉換器進行采樣和轉換同時該隨機脈沖信號經放大、限幅并整形后的脈沖信號(Vout)送高速輸入器件的HSI0、HSIl端,作為脈沖前后沿的觸發事件,啟動中斷處理程序。HSI0輸入端作為脈沖信號的前沿(上升沿)事件觸發輸入端,用于讀出并記錄脈沖前沿到達的時刻及啟動A/D轉換器進行采樣和轉換;HSIl輸入端作為脈沖信號的后沿(下降沿)事件觸發輸入端,用于讀出并記錄脈沖后沿到達的時刻及讀取A/D轉換器的值。另外整形后的脈沖信號(Vout)有一路信號(CLKl)送到一組7415374(4片)的CLK端,用于鎖存74Lsl61計數器的計數值(即脈沖前沿到達的時刻)。通過反相器輸出的另一路信號(CLK2)送到另74LS374(4片)的CLK端,用于鎖存74LSl61計數器的計數值(即脈沖后沿到達的時刻)。脈沖信號的寬度即為2個計數值的差值。

3.2 高速信號采集及存儲電路

高速信號采集及存儲電路用于采集卡在采集方式下時采集輸入脈沖的脈內波形數據。采用8位高速A/D轉換器TLC5540,其最大轉換速度40 MS/s,模擬輸入帶寬大于75 MHz,具有內部采樣和保持功能。

TLC5540進行轉換所需時鐘信號頻率可由單片機設置。A/D轉換后的數據自動存儲在外接的62256存儲器中,其地址信號由4個74LSl61產生。其工作原理為:首先QCLR輸出一個負脈沖,將74LSl61計數器清零,然后再設置采樣時鐘信號(TCLK),啟動TLC5540進行轉換,同時將RAD信號設為有效(低電平),產生的數據在脈沖信號(Vout為高電平)出現時按順序寫入外接的62256存儲器中,脈沖信號(Vout為低電平)消失則自動停止寫入。高速RAM的地址信號由74LSl61地址產生器提供。對每個脈沖信號期間采樣的次數可根據2個脈沖信號最后寫入地址的差值進行來計算,即由單片機讀出的該脈沖信號下降沿時刻74LSl61的計數值(即最后寫入的RAM的地址),再減去上一次讀出的值,即為該脈沖的采樣次數。連續采樣一群脈沖的波形數據后需暫停采集,將采集的每個脈沖的波形數據與該脈沖的其他參數(如脈沖寬度、脈沖到達時間等)按規定的格式組合后送到與主機交換數據的FIF0高速存儲器中,供主機讀取和處理,數據送完后再啟動采集下一群脈沖。一群脈沖的數量由用戶根據實際情況確定,以連續采集的波形數據存入高速RAM中不產生溢出為最大限。圖4為高速信號采集及存儲電路。

評論