高速高精度鐘控比較器的設計

1.2 鐘控比較級

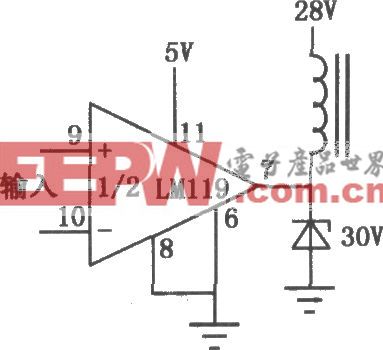

鐘控比較級響應時間的快慢直接影響著比較器的速度。該部分電路的原理主要是利用預放大器的輸出控制比較級輸入端電壓的變化,即通過預放大級電路將比較器輸入差值放大到大于比較級的閾值,避免了比較級的非穩態輸出,從而把再生階段初始時建立的較小的輸入電壓差在短時間內再生放大,提高了比較器的精度。該鐘控比較級(圖1)的兩個交叉耦合MOS管VM10、VM11的互聯實現了用正反饋環路結構提高比較級電路增益的目的。開關晶體管VM4、VM5、VM12、VM13、VM14、VM15共同控制比較級的工作狀態,狀態轉換的快慢影響著比較級的再生速度,MOS開關的響應時間為![]() ,因此可以通過減小晶體管的尺寸來縮短比較級的再生時間,本設計中的開關晶體管均采用該工藝下最小尺寸。

,因此可以通過減小晶體管的尺寸來縮短比較級的再生時間,本設計中的開關晶體管均采用該工藝下最小尺寸。

比較級電路有兩種工作模式:復位模式與比較模式。當時鐘信號clk為高電平時,VM4、VM5導通使預放大器采集并放大輸入信號,VM12、VM13導通和VM14、VM15關斷強制將再生節點電壓Vo1,Vo2拉到低電平。當時鐘信號clk為低電平時,VM4、VM5、VM12、VM13關斷,VM14、VM15導通,系統進入比較模式。VM10和VM11柵源電壓的不同將導致流過這兩個晶體管電流的不同,兩再生節點Vo1,Vo2電壓上升的快慢就不同,電壓上升較快的一端將會抑制另一端再生節點電壓的上升,比較級電路正反饋的機制將會使再生節點電壓差迅速增加。

1.3 輸出緩沖級

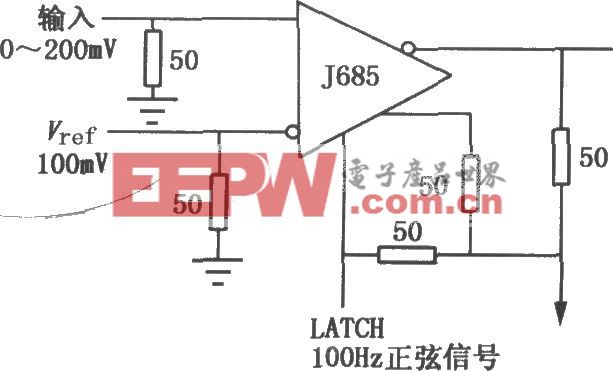

目前,A/D轉換器中的比較器通常在時鐘的跳變沿處進行比較。本文設計的電路是通過在比較級電路后增加輸出緩沖級(又稱后放大級) ——正反饋的latch結構來實現的,其主要作用是把比較級電路的輸出信號轉化為邏輯電平(O V或5 V)。

當使能信號enable為低電平時,VM24關斷(圖1),再生節點電壓無法作用于輸出緩沖級電路,整個比較系統處于不工作狀態。當enable為高電平時,VM24導通,輸出緩沖級電路導通。當時鐘信號clk為低電平時,VM18和VM19導通,VM16、VM17、VM20、VM21構成了一個首尾相接的放大器,根據比較級再生節點電壓的不同將比較器的輸出電壓VOUT1,VOUT2迅速轉化為全擺幅數字電平。當clk為高電平時,VM18和VM19關斷,緩沖級電路進入鎖存輸出信號的狀態,保證了輸出結果的穩定性。

2 電路的分析和優化

2.1 比較速度

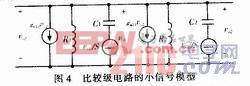

在時鐘信號clk為低電平時,鐘控比較級電路進入再生階段,此時該部分電路的小信號模型,如圖4所示。

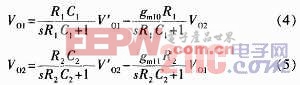

根據小信號模型的節點電流可得到如下公式:

其中,C1和C2是從VM10和VM11的漏極到地的電容,R1和R2是從VM10和VM11的漏極到地的電阻,![]() 為再生節點所加的初始電壓。τ為時間常數,假設所有的晶體管相同,則有R1=R2,C1=C2,gm11=gm10=gm,從而τ1=τ2=τ。

為再生節點所加的初始電壓。τ為時間常數,假設所有的晶體管相同,則有R1=R2,C1=C2,gm11=gm10=gm,從而τ1=τ2=τ。

用△Vo定義Vo1與Vo2的差值,用△Vi定義![]() 的差值,因此

的差值,因此

需要注意的是:1)在鐘控比較級使能之前,再生節點電壓變化的速度隨△Vi的增加而增大;2)τ的絕對值越小,傳輸延時越小,比較器工作速度越快。由此可知,通過增加輸入跨導、減小輸出節點的負載電容和提高初始輸入電壓差可提高比較器速度。

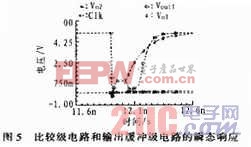

此外,存比較級電路后增加的輸出緩沖級電路也能縮短比較器的比較時間。其優點是結合了比較級電路的正指數響應和正反饋latch結構的負指數響應,即比較級電路先經過一時間段將輸入信號放大到某一差值Vx,輸出緩沖級電路就會迅速將比較器的輸出電壓轉化到邏輯電平。本文設計的比較級電路和輸出緩沖級電路的瞬態響應如圖5所示。

2.2 回饋噪聲

在比較級電路工作階段,再生節點電壓的快速變化通過寄生電容對輸入信號引起的干擾稱為回饋噪聲,其嚴重影響比較器的精度。在模數轉換器中會用到大量的比較器,這些比較器上的回饋噪聲將提高ADC的誤碼率。為了有效地抑制回饋噪聲對比較器的影響,本文采用了隔離和互補技術。

在預放大級中增加開關晶體管VM4和VM5,實現了隔離輸入信號與再生節點電壓的回饋噪聲。在比較器從復位階段轉變為比較階段時,VM 4、VM5關斷,切斷了預放大器和比較級電路之間的信號通路,使再生節點電壓的快速變化無法直接耦合到比較器的輸入端,從而降低了回饋噪聲。

互補技術的具體實現方法是在預放大級的輸入端增加NMOS管VM25、VM26構成的電容,使其與輸入晶體管VM1、VM2的柵漏電容CGD構成互補結構。為達到最佳互補效果,CM25,CM26的值應與CGD保持相等,即VM25、VM26的寬度應為VM1、VM2的一半。當輸入對管源端電壓發生變化時,CM25,CGD-M2和CM26,CGD-M1構成的互補結構使變化的電流相互抵消,從而提高輸入電壓的穩定性。

評論